### 博士論文

Bio-inspired Electronic Circuits and Stochastic Information Processing Systems exploiting Noise and Fluctuations ゆらぎを利用する生物的な電子回路と確率的情報処理システム に関する研究

> Graduate School of Information Science and Technology Hokkaido University 北海道大学 大学院情報科学研究科

> > Gonzalez-Carabarin Lizeth ゴンザレス カラバリン リセス Jan. 2015

#### Abstract

Current technological demands look for smaller, faster and more efficient systems. However, such demands are limited mainly by physical properties of devices (e.g. size of transistors, increase of electrical noise, etc.). At this point alternative solutions may have a response for such demands. The study of biological systems may offer a different perspective to fulfill such requirements. Biological structures have been optimized during millions of years of evolution resulting in power-efficient, fast and compact systems that are resilient against noisy and hostile environments. Although, no electrical system has been able to emulate any biological structure in their totality, neuromorphic systems have already proved to be efficient in many engineering applications.

This thesis is inspired specifically by how some biological structures use noise to improve determined tasks. The utilization of noise to enhance performance is a wellstudied phenomenon and it is known as Stochastic Resonance (abbreviated as SR). Examples of SR in nature are found inside mechanoreceptors of some insects and fishes to detect weak signals from the environment, it is also observed in the human sensory system, as well as at molecular level to detect low-amplitude stimuli inside nervous system. And at system level, it is also involved in the evolution of human creativity, imagination and decision-making processes. At large-scale natural phenomena, SR has an effect in the ice age transitions.

The use of noise to improve certain tasks could seem counterintuitive from the electrical engineering point of view; however nature has given us many examples of the positive utilization of noise. Noise and fluctuations are inherently part of nature; and biological systems have already self-adapted to include external and internal fluctuations in their processing as a positive factor; in this sense, SR has been already exploited by biomedical engineers, just to mention some remarkable examples on the improvement of silicon cochlea, balance control systems and life-support ventilators, where the introduction of noise is a key factor for a more precise emulation of these artificial systems. Moreover, it has been also utilized in engineering systems such as electrical sensors to detect weak stimuli, signal amplification and noise-induced synchronization circuits.

In this thesis it is presented two main applications related with SR and its applications. The first case is based on the study on how electrical spikes are transmitted along long axons inside the nervous systems. In this process, due to the variability of conductance among stages, the amplitude of electrical spikes may not be enough to excite next stage. However, it has been discovered that internal fluctuations inside node axons may enhance signal transmission. This idea could be mimicked by electrical systems to transmit signals efficiently in the presence of mismatches. Simulation results show that with the introduction of an optimal amount of noise, signal transmission is improved in the presence of mismatches.

The second part presents a novel application of the SR effect in the field of digital systems. Considering the problems that current devices are facing due to an increment of parameter variability (it may provoke malfunction of electrical chips) and demands for lowering their power, it is utilized noise to design logic gates with three main characteristics: low-power consumption, parameter-variability tolerance and a stable output regardless the introduction of noise. These gates were called stochastic resonance gates or simply SR gates. Simulations and experimental results show their effective performance on the recovery of logic functions in the presence of parameter variations of transistor (such as threshold voltage). However, due to their dependence on stochastic processes, their response presents an unpredictable delay. Therefore the most suitable application is found in the field of asynchronous circuits to design delay-insensitive circuits. Therefore the third part of this study is concentrated in the application of the SR gates to design asynchronous circuits. Synchronous circuit designs have been offering a robust solution for many years, however, considering the current challenges of VLSI circuits, asynchronous circuits may offer a better solution for designing faster, smaller and less power consuming circuits.

Finally, biological systems work inherently in noisy environments and during years of evolution they have self-adapt to these conditions, either by avoiding it or including it as a beneficial part. Towards the next generation of processors, to design more noiseresilient and efficient circuits, a positive collaboration of noise and fluctuations could be a necessary stage to achieve it.

# Contents

| 1        | Inti           | roduct  | ion                                                      | 9  |

|----------|----------------|---------|----------------------------------------------------------|----|

|          | 1.1            | Backg   | ground and motivation                                    | 9  |

|          | 1.2            | Objec   | tives and thesis organization                            | 12 |

|          | Refe           | erences |                                                          | 16 |

| <b>2</b> | Bio            | logical | l-inspired noise-driven phenomena and computing          | 19 |

|          | 2.1            | Noise   | in nature                                                | 19 |

|          |                | 2.1.1   | Influence of noise on animal physiology                  | 19 |

|          |                | 2.1.2   | Influence of noise on human perception                   | 20 |

|          |                | 2.1.3   | Influence of noise on human brain                        | 21 |

|          | 2.2            | Stoch   | astic resonance                                          | 23 |

|          |                | 2.2.1   | Definition                                               | 23 |

|          |                | 2.2.2   | Stochastic resonance in bistable systems                 | 24 |

|          |                | 2.2.3   | Stochastic resonance in non-dynamical systems            | 26 |

|          |                | 2.2.4   | Suprathreshold stochastic resonance                      | 26 |

|          |                | 2.2.5   | Applications of stochastic resonance                     | 27 |

|          | Refe           | erences |                                                          | 30 |

| 3        | $\mathbf{Spi}$ | ke trai | nsmission assisted by noise                              | 35 |

|          | 3.1            | Biolog  | gical background: spike transmission in nervous system   | 35 |

|          | 3.2            | Excita  | able models                                              | 36 |

|          |                | 3.2.1   | FitzHugh-Nagumo model                                    | 38 |

|          | 3.3            | Noise   | -assisted spike transmission along excitable circuits    | 45 |

|          |                | 3.3.1   | Circuit design                                           | 45 |

|          |                | 3.3.2   | Simulations and results                                  | 47 |

|          |                | 3.3.3   | Stochastic-resonance-like behavior from subthreshold and |    |

|          |                |         | suprathreshold internodal resistances                    | 52 |

|          | Refe           | erences |                                                          | 54 |

| <b>4</b> | Noi  | se-driv         | ven digital circuits                                             | 57   |

|----------|------|-----------------|------------------------------------------------------------------|------|

|          | 4.1  | Config          | guration of an operational amplifier with hysteresis $\ldots$ .  | 57   |

|          | 4.2  | Floati          | ng Gate MOSFET                                                   | 58   |

|          | 4.3  | Desig           | n of stochastic-resonance logic gates                            | 60   |

|          |      | 4.3.1           | Circuit design                                                   | 60   |

|          |      | 4.3.2           | Mathematical model of stochastic-resonance logic gates           | 64   |

|          | 4.4  | Simula          | ation results                                                    | 68   |

|          |      | 4.4.1           | Performance of the stochastic-resonance logic gates              | 68   |

|          |      | 4.4.2           | Experimental results: stochastic-resonance logic gates based     |      |

|          |      |                 | on an operational amplifier                                      | 72   |

|          |      | 4.4.3           | Delay time of the stochastic-resonance logic gates               | 73   |

|          | Refe | erences         |                                                                  | 76   |

| <b>5</b> | Ap   | plicatio        | ons of stochastic resonance logic gates: Asynchronou             | ıs   |

|          | circ | $\mathbf{uits}$ |                                                                  | 79   |

|          | 5.1  | Defini          | tion of asynchronous circuits                                    | 79   |

|          | 5.2  | Basic           | concepts                                                         | 82   |

|          |      | 5.2.1           | Delay models                                                     | 83   |

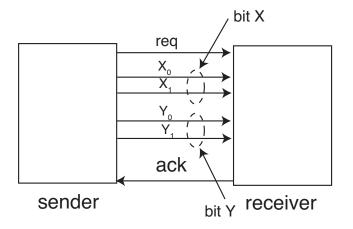

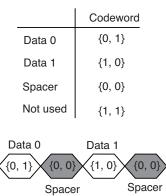

|          |      | 5.2.2           | Data encoding                                                    | 83   |

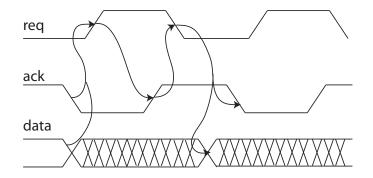

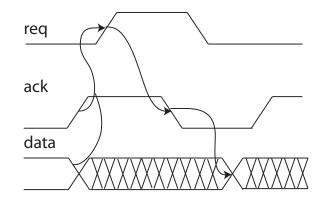

|          |      | 5.2.3           | Communication protocols                                          | 85   |

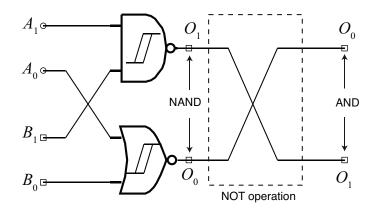

|          | 5.3  | Dual-1          | rail gates based on stochastic-resonance logic gates $\ldots$ .  | 86   |

|          |      | 5.3.1           | Circuit design                                                   | 86   |

|          |      | 5.3.2           | Simulation results                                               | 86   |

|          | 5.4  | Async           | chronous logic components with hysteresis $\ldots \ldots \ldots$ | 87   |

|          | 5.5  | Async           | chronous pipelines                                               | 89   |

|          | 5.6  | Async           | chronous pipelines based on stochastic-resonance logic gates .   | 91   |

|          |      | 5.6.1           | Circuit design                                                   | 91   |

|          |      | 5.6.2           | Simulation results                                               | 91   |

|          | 5.7  | Imple           | mentation of asynchronous pipelines based on stochastic-reson    | ance |

|          |      | gates           | utilizing an operational amplifier                               | 93   |

|          |      | 5.7.1           | Circuit design                                                   | 93   |

|          |      | 5.7.2           | Experimental results                                             | 94   |

|          | Refe | erences         |                                                                  | 98   |

| 6        | Cor  | nclusio         | ns                                                               | 101  |

| A        | ckno | wledgr          | nents                                                            | 103  |

List of publications

# List of Figures

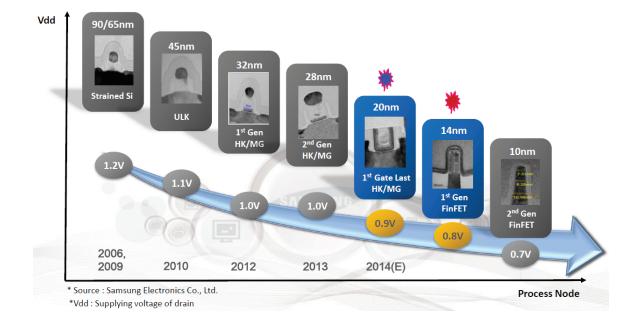

| 1.1 | Roadmap of transistor miniaturization $[10]$                                                            | 10 |

|-----|---------------------------------------------------------------------------------------------------------|----|

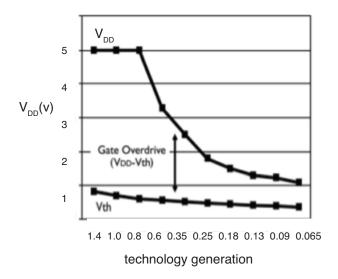

| 1.2 | Trend of supply voltage and threshold voltage scaling                                                   | 10 |

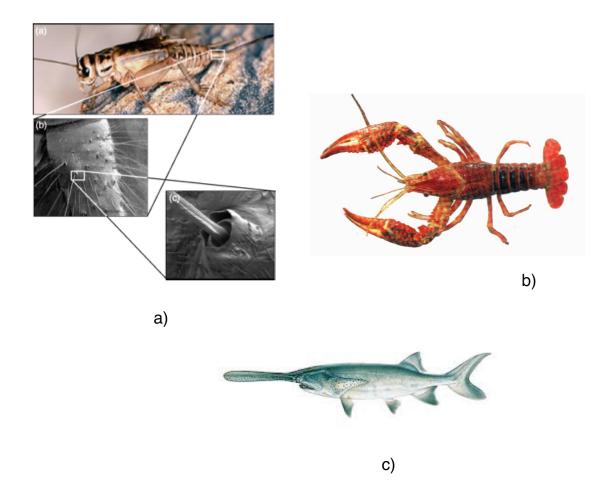

| 2.1 | Examples of beneficial role of noise in animal kingdom: (a) cricket's                                   |    |

|     | hair, (b) crayfish and (c) paddlefish's sensory systems                                                 | 20 |

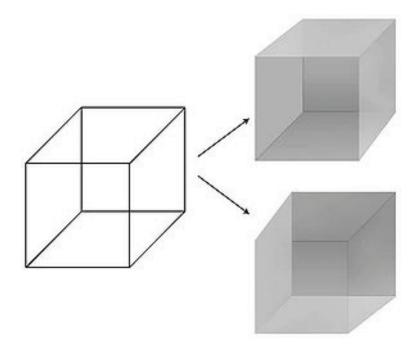

| 2.2 | Necker cube, an example of a perceptual bistable process $\ldots$ .                                     | 22 |

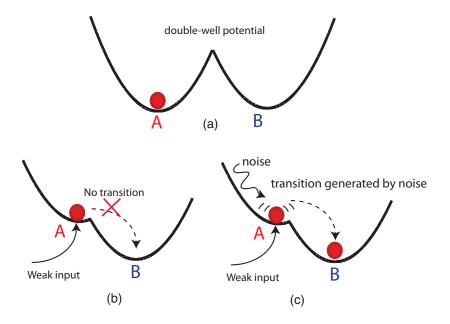

| 2.3 | Particle in a double-well potential under the influence of noise: (a)                                   |    |

|     | system in equilibrium, (b) system under the influence of a weak-                                        |    |

|     | periodic external signal (no transition), and (c) noise-assisted tran-                                  |    |

|     | sition                                                                                                  | 24 |

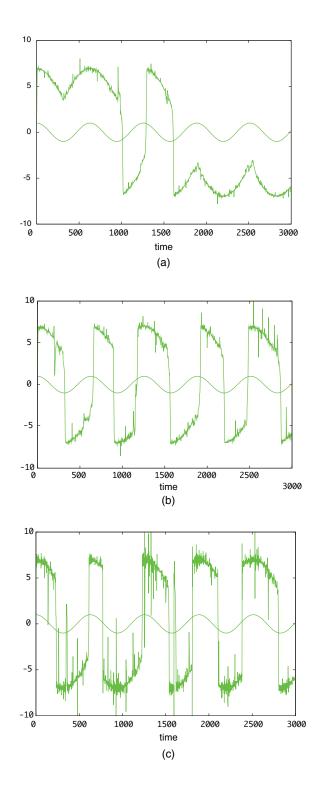

| 2.4 | Noise-assisted transition in a double-well potential: (a) low inten-                                    |    |

|     | sity noise (b) optimal amount of noise (c) high amplitude noise                                         | 25 |

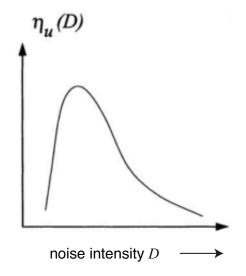

| 2.5 | Characteristic curve Signal to Noise Ratio (SNR) exhibiting SR $$ .                                     | 27 |

| 2.6 | Non-dynamical SR                                                                                        | 27 |

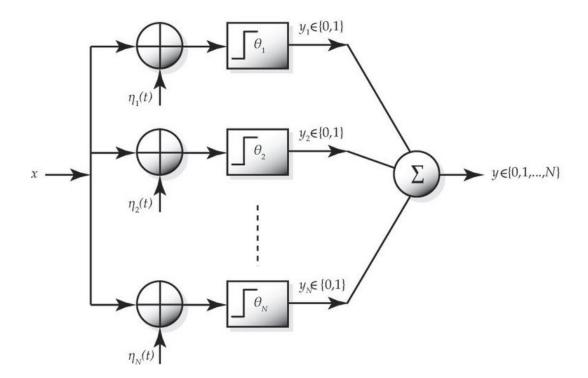

| 2.7 | Suprathreshold SR system                                                                                | 28 |

| 3.1 | Basic model of transmission line in non-uniform medium                                                  | 36 |

| 3.2 | General scheme of myelinated axons                                                                      | 37 |

| 3.3 | FitzHugh-Nagumo circuit.                                                                                | 38 |

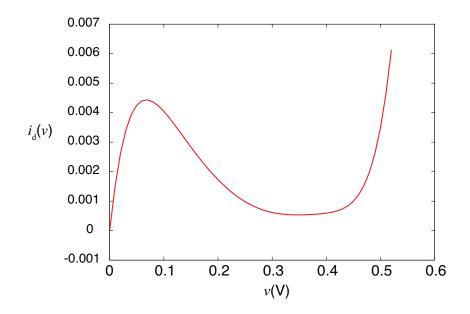

| 3.4 | Plot of the $i$ - $v$ characteristic of the diode utilized to simulate the                              |    |

|     | FitzHugh-Nagumo circuit, where clearly a cubic function is observed                                     | 40 |

| 3.5 | v-nullcline and $i$ -nullcline for the circuit of Fig. 3.3                                              | 41 |

| 3.6 | Four different areas are shown, according to the fixed point of                                         |    |

|     | v-nullcline and $i$ -nullcline, where the direction of the vector field                                 |    |

|     | depends on the regions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 42 |

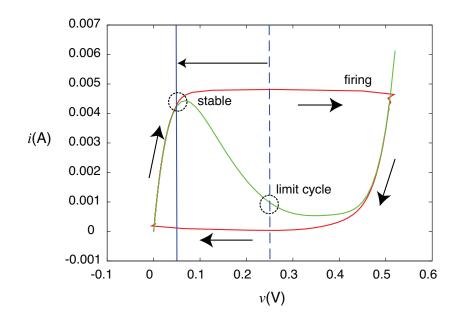

| 3.7 | Parametric plot of $i$ versus the membrane potential $v$ , where clearly                                |    |

|     | its trajectory is represented by a limit cycle, according to the circuit                                |    |

|     | parameters                                                                                              | 43 |

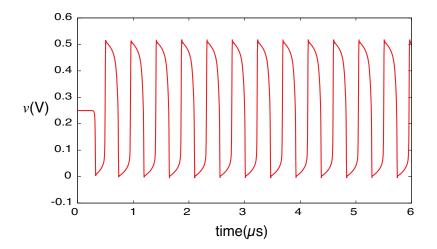

| 3.8 | Spike-like membrane potential $v$                                                                       | 43 |

|     |                                                                                                         |    |

| 3.9  | Parametric plot of $i$ versus the membrane potential $v$ , where the new fixed point is stable $\ldots \ldots 4$                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

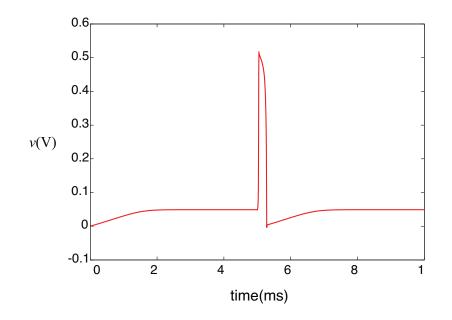

| 3.10 | Spike-like membrane potential, after firing, the state returns to an stable state $v$                                                                                                                                                                             |

| 3 11 | Noise-driven FitzHugh-Nagumo circuit                                                                                                                                                                                                                              |

|      | Block diagram of serially-connected circuits with noise-assisted                                                                                                                                                                                                  |

| 3.13 | spike propagation                                                                                                                                                                                                                                                 |

|      | without noise assistance (a) and its phase portrait (b) 4                                                                                                                                                                                                         |

| 3.14 | Spike-like potential at 1st, 5th, 7th and 9th circuit with noise as-<br>sistance (a) and its phase portrait (b)                                                                                                                                                   |

| 3.15 | Generated spike train assisted by noise at (a) 1st circuit, (b) 5th circuit, (c) 7th circuit, and (d) 9th circuit                                                                                                                                                 |

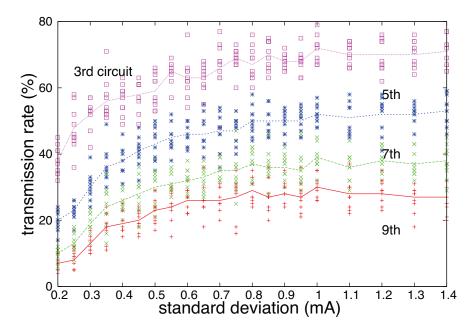

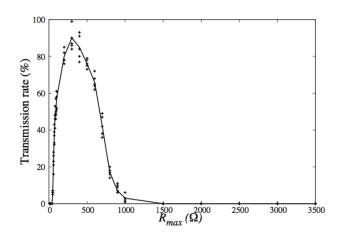

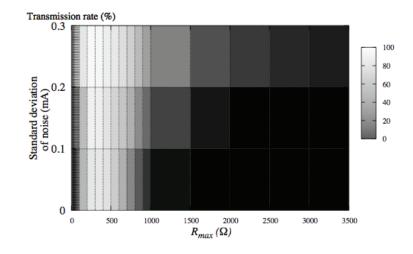

| 3.16 | Percentage of successful spikes versus standard deviation of noise                                                                                                                                                                                                |

| 3.17 | (mA)                                                                                                                                                                                                                                                              |

| 3.18 | Spike transmission rate versus standard deviation of internodal resistor $k\Omega$ and standar deviation of noise (mA)                                                                                                                                            |

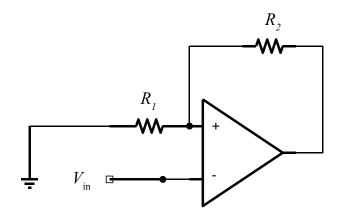

| 4.1  | Schmitt-trigger operational amplifier configuration                                                                                                                                                                                                               |

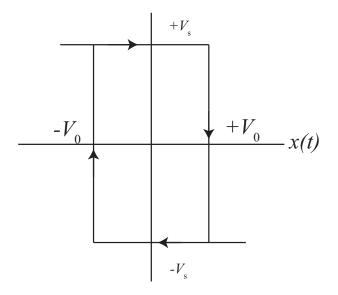

| 4.2  | Typical hysteresis characteristic of a Schmitt-trigger circuit 5                                                                                                                                                                                                  |

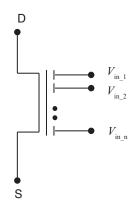

| 4.3  | Symbol for the Floating Gate MOSFET                                                                                                                                                                                                                               |

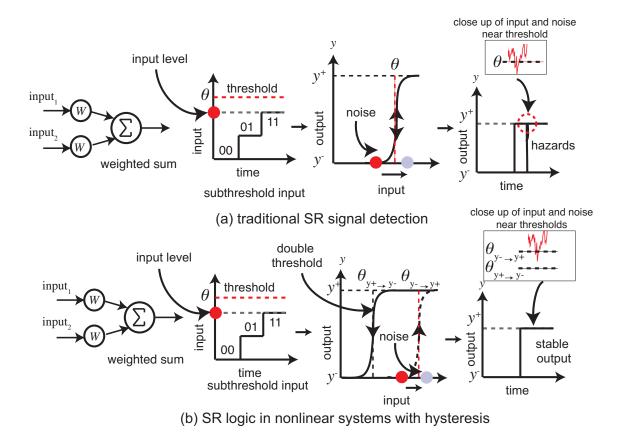

| 4.4  | Noise assistance in nonlinear systems with one threshold (a), noise assistance in nonlinear systems exhibiting hysteresis (b) 6                                                                                                                                   |

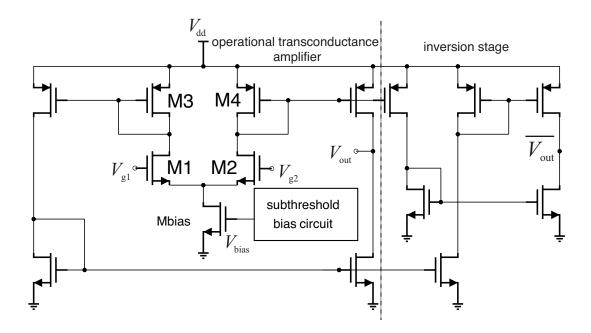

| 4.5  | CMOS design of the subthreshold operational transconductance<br>amplifier (OTA)                                                                                                                                                                                   |

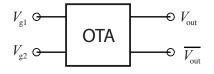

| 4.6  | Generic symbol of an OTA.                                                                                                                                                                                                                                         |

| 4.7  | Construction of the proposed SR gate configuration for the basic logic operations. The configuration depends on the values of $V_{\text{bias1}}$                                                                                                                  |

| 4.8  | and $V_{\text{bias}2}$                                                                                                                                                                                                                                            |

|      |                                                                                                                                                                                                                                                                   |

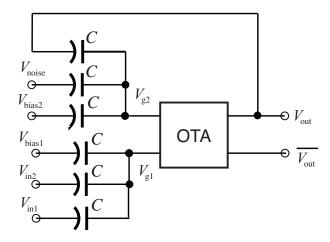

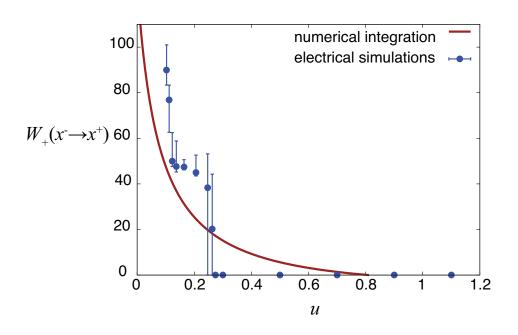

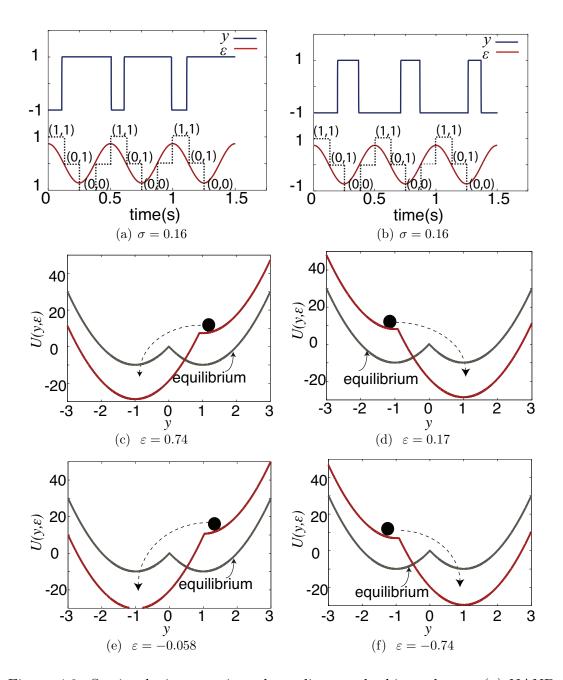

| 4.9  | Setting logic operations depending on the bias value $\alpha$ : (a) NAND<br>operation, and (b) NOR operation; (c) and (d) are the double-<br>well potential function for NAND operation; (e) and (f) are the<br>double well potential function for NOP expection. |

|      | double-well potential function for NOR operation 6                                                                                                                                                                                                                |

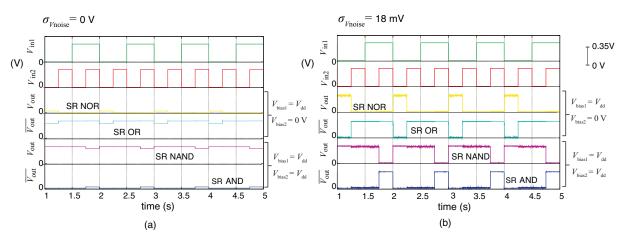

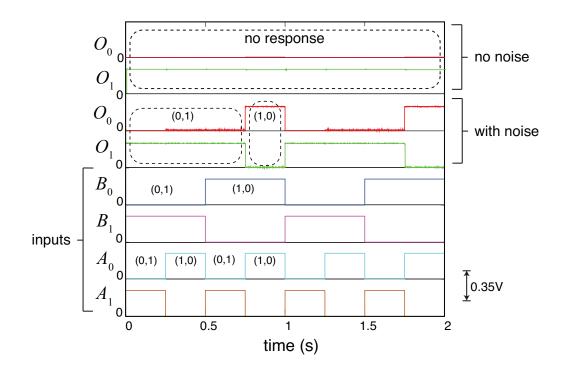

| 4.10 | Simulation results of an SR gate for NOR, OR, NAND and AND                                     |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | operations. (a) without noise, the logic operations are not gener-                             |     |

|      | ated. (b) with an optimal amount of noise, the logic operations                                |     |

|      | are generated correctly                                                                        | 68  |

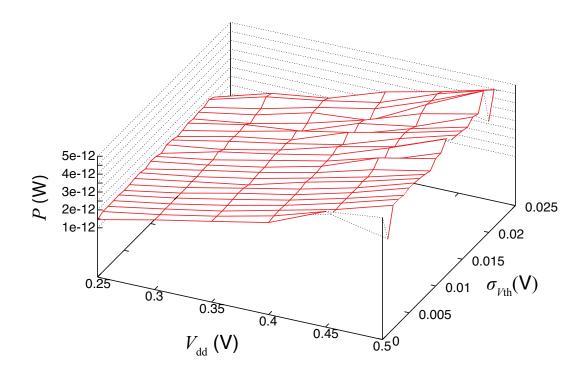

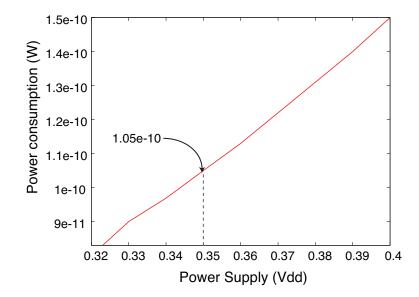

| 4.11 | Power consumption $P$ versus the power supply $V_{dd}$ and the stan-                           |     |

|      | dard deviation of $V_{\rm th}$                                                                 | 69  |

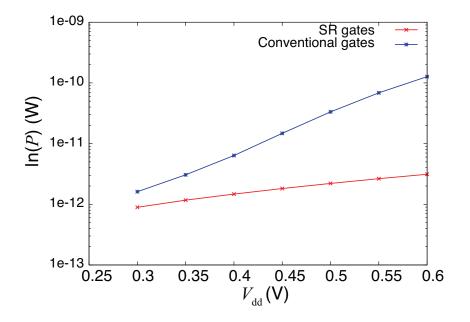

| 4.12 | Power consumption of a conventional NAND gate and a SR NAND                                    |     |

|      | gate                                                                                           | 70  |

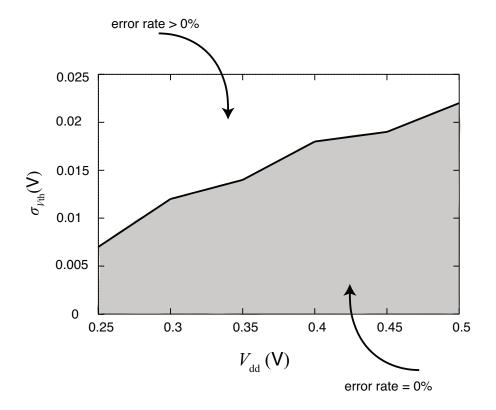

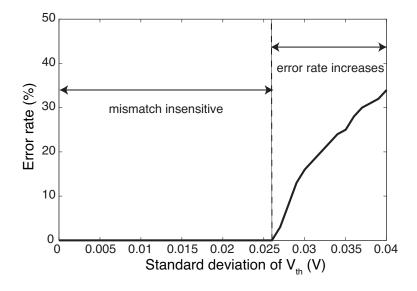

| 4.13 | Phase diagram of the SR NAND gate error rate versus $V_{\rm dd}$ and $\sigma_{V_{\rm th}}$     | 71  |

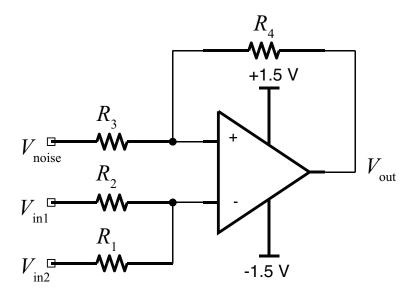

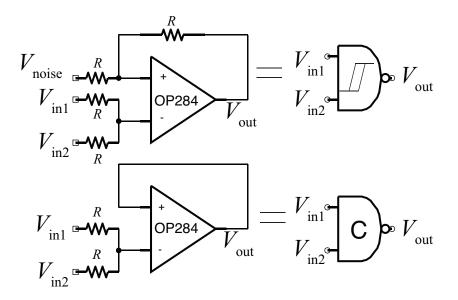

|      | OP284 with a positive feedback configuration.                                                  | 72  |

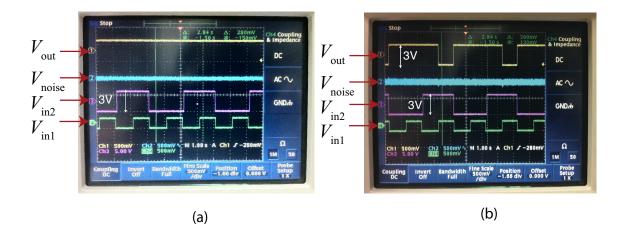

| 4.15 | Experimental results of the SR gates: (a) low amplitude of noise,                              |     |

|      | not enough to detect the signal, and (b) shows the minimum stan-                               |     |

|      | dard deviation to effectively detect the signal                                                | 72  |

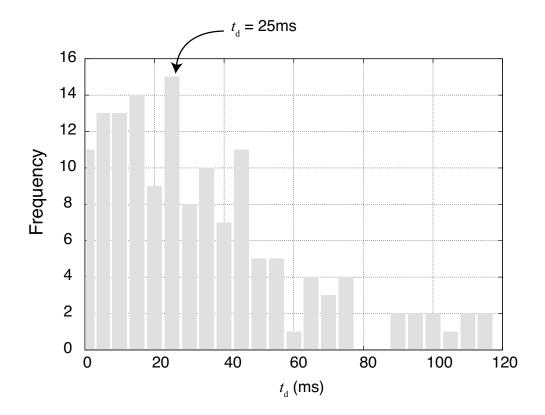

| 4.16 | Histogram for the delay time $t_d$ of the response of the SR NAND                              |     |

|      | gate                                                                                           | 74  |

| ~ -  |                                                                                                | ~ ~ |

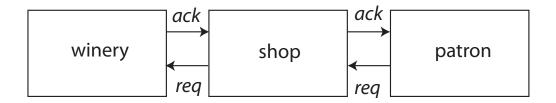

| 5.1  | Analogy of asynchronous circuits with a winery-shop-patron example                             |     |

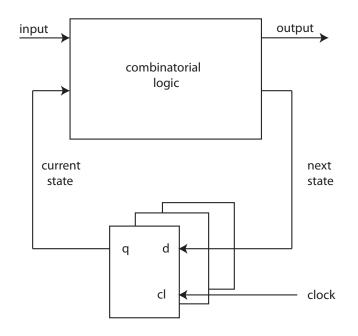

| 5.2  | Synchronous circuit general scheme                                                             | 81  |

| 5.3  | Asynchronous circuit general scheme                                                            | 82  |

| 5.4  | Bundle data encoding                                                                           | 84  |

| 5.5  | Dual-rail data encoding                                                                        | 84  |

| 5.6  | Dual-rail data representation                                                                  | 85  |

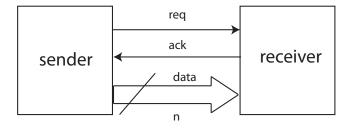

| 5.7  | Four-phase protocol                                                                            | 85  |

| 5.8  | Two-phase protocol                                                                             | 86  |

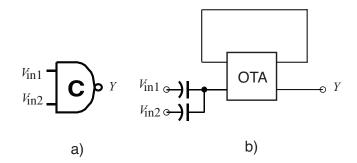

| 5.9  | Dual-rail SR AND/NAND gate                                                                     | 87  |

| 5.10 | SPICE simulations for the dual-rail SR AND/NAND gate (case                                     |     |

|      | with noise)                                                                                    | 88  |

| 5.11 | Electrical symbol for the C-element (b), and implementation of the                             |     |

|      | C-element using an OTA (b)                                                                     | 88  |

| 5.12 | Simulation results for the C-element.                                                          | 89  |

| 5.13 | Muller pipeline                                                                                | 90  |

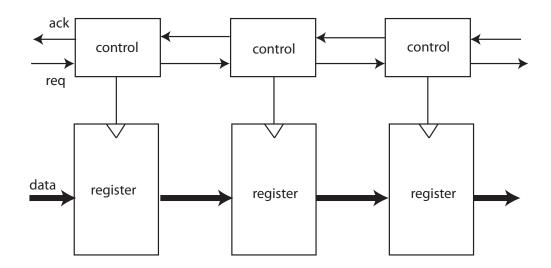

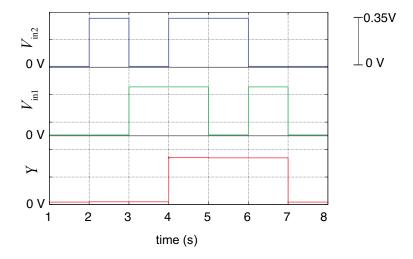

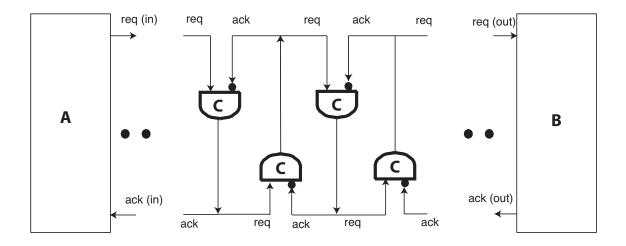

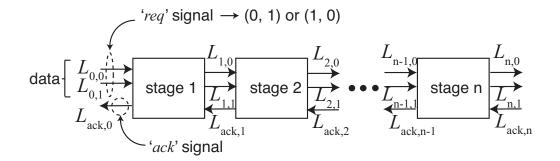

| 5.14 | WCHB pipeline diagram block                                                                    | 92  |

| 5.15 | Three-stage WCHB asynchronous pipeline                                                         | 92  |

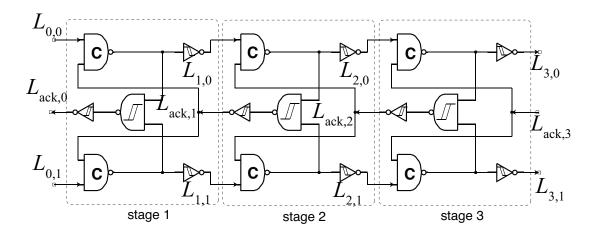

| 5.16 | SPICE simulations for the WCHB asynchronous pipeline based on                                  |     |

|      | SR logic gates (case with noise) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$            | 93  |

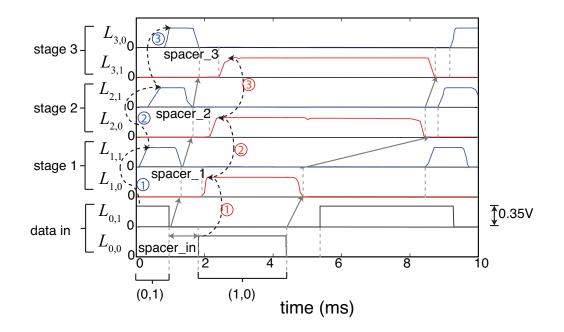

| 5.17 | Control signals between stages 1 and 2 of the WCHB asynchronous $% \left( {{{\rm{A}}} \right)$ |     |

|      | pipeline                                                                                       | 94  |

| 5.18 | Power consumption of the three stage WCHB asynchronous pipeline                                     |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | 95                                                                                                  |    |

| 5.19 | Error rate versus $\sigma_{V_{\rm th}}$ (V)                                                         | 95 |

| 5.20 | OP284 configuration to implement the SR NAND gate and the                                           |    |

|      | C-element $\ldots$ | 96 |

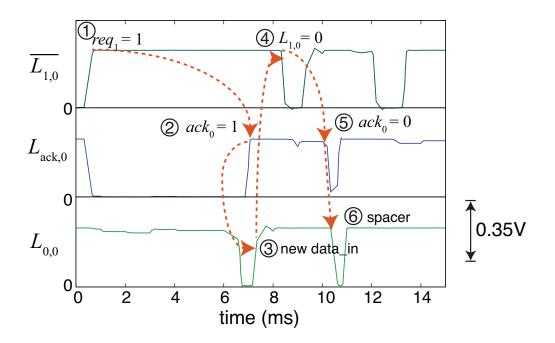

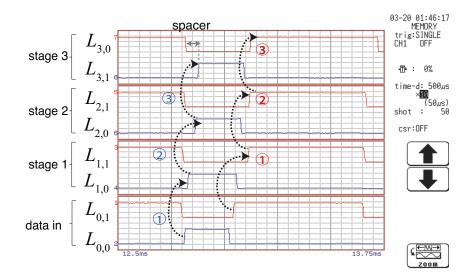

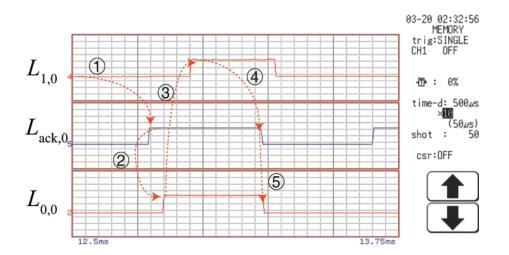

| 5.21 | Experimental results for the three-stage WCHB asynchronous pipeline                                 |    |

|      | (data transmission), obtained from a Memory Hicorder HIOKI                                          |    |

|      | 8826                                                                                                | 96 |

| 5.22 | Experimental results for the three-stage WCHB asynchronous pipeline                                 |    |

|      | (acknowledge signal between two stages)                                                             | 97 |

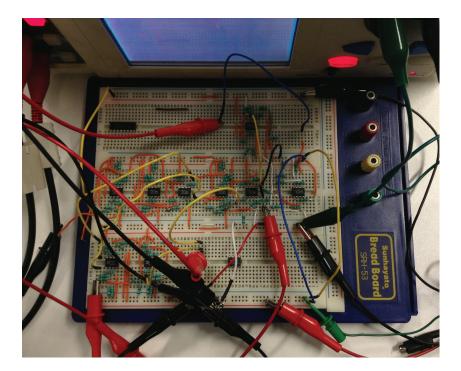

| 5.23 | Breadboard implementation of the three-stage WCHB asynchronous                                      |    |

|      | pipeline based on OP284 $\ldots$                                                                    | 97 |

# List of Tables

| 4.1 | Selection of the logic operations according to $V_{\text{bias1}}$ and $V_{\text{bias2}}$ as |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | well as $V_{\text{out}}$ and $\overline{V_{\text{out}}}$                                    | 63 |

| 5.1 | C-element state table with input voltages mapped as logic inputs                            | 87 |

## Chapter 1

# Introduction

### 1.1 Background and motivation

With the continuus miniaturization of conventional transistors, electrical chips have acquired smaller sizes with higher performance demands. However, as their physical dimensions have been shrunk, atomic dimensions have been reached (Fig. 1.1). At this point, many aspects of their performance are deteriorated [1–8].

Physical geometry patterns for lithography can not be printed reliably, resulting in severe degradation in device matching. It is predicted that in coming years, 14nm and 7nm technologies will be implemented with emerging devices; moreover, current oxide thickness is equivalent to 5 molecular layers of oxide, and by 2019 it is expected to be reduced by half. This gives as a results an increment on the leakage current due to the increase of oxide tunnel currents and decrease of threshold voltage. Leakage increment and gain decrement represent a challenge for designers, since they may seriously influence the functionality of the chip if the traditional designing methods are used. Moreover to fulfill the demands related with power reduction, supply and threshold voltage must be scaled also [9] (Fig. 1.2).

In the case of digital systems, new challenges are faced, such as energy-delay optimization, clock and power distribution. With demands for increasing performance, there is a dilemma between the necessity of an increment of power supply and the reduction of energy consumption.

In the case of analog systems, device matching became a key factor in the chip functionality, and more accurate models of devices are needed [11–13]. From the physical point of view there are many proposed solutions to integrate transistors at nanoscale to avoid problems such as the increment of tunneling current, de-

Figure 1.1: Roadmap of transistor miniaturization [10]

Figure 1.2: Trend of supply voltage and threshold voltage scaling.

creasing line delays and so on [14, 20]. Some of these solutions have already been integrated by using new materials in combination with the conventional CMOS technology.

There is also plenty of research done regarding promising devices that may substitute traditional MOS transistor and perform better at nanoscale sizes. Although the new 'holy grail' of electronics that could substitute MOS transistors definitively have not appeared yet, different alternatives have been explored, such as nanowire (NW) transistors [15], carbon nanotube field-effect transistors (CNT-FETs) [16], graphene nano ribbon (GNR) transistor [17], single-electron transistors (SETs) [18], and quantum-dot cellular automata (QCA) [19], just to mention some examples.

From the design point of view, different strategies have been proposed as well, and these approaches are applied both to circuit and system levels [21]. Considering current state of nanoscale MOS transistors and emerging devices, demands for lowering power consumption and increasing robustness, in terms of parameter variabilities are presented in both cases, therefore our motivation is focused on studying different design strategies.

In this sense, many design strategies have been proposed out of traditional metdologies [22–24]. One of the most prominent areas is neuromorphic engineering. Nature designs have evolved during millions of years to produce compact, efficient and low-power consumption designs. Nature is inevitably surrounded by adverse environments, however nature designs seem to be resilient against this problem. How natural designs have accomplished to be successful into such a hostile environments? Many efforts have been made to answer this question. It is known that biological system are not deterministic systems but instead, they are the result of a combination of many factors (internal and external), that together produce complex systems governed by stochastic processes. It has been studied that fluctuations are responsible in many cases for assisting the realization of determined tasks, such as sensing and improving signal transmission in many biological structures. Therefore our motivations arise from the biological point of view.

The combination of nonlinear systems and the addition of weak periodic signals with additional noise is a well-studied phenomenon, known as Stochastic Resonance (SR). Among the applications of SR phenomena, electrical engineering is the key one. Although the use of noise to improve certain tasks is not part of the common sense knowledge among electrical engineers, it has been already demonstrated that noise-driven circuits can performer better in determined tasks. This kind of circuits (as well as many new promising devices) are affected by the presence of delays that may provoke problems as clock skew and jitter in the case of synchronous circuits, that represents the key basis for most of current electrical chips; synchronous circuits are fast, robust and own a relatively easy design methodology. But as nano scales are reached, synchronization problems may arise. Therefore as a second motivation, the study of asynchronous circuits may be useful as an alternative to design delay-insensitive circuits.

### **1.2** Objectives and thesis organization

Following the motivations mentioned in previous paragraphs, the objectives of this thesis are based on the study on how noise is beneficial in some biological structures, and how these idea could be mapped in engineering to reduce power consumption and increase robustness against variabilities. Enclosed in this point, three main topics are explored:

- 1. Exploration on how biological structures, like nervous systems transmit spikes along long paths in the presence of conductance mismatches. Variations on conductances usually provoke spike transmission to be stopped. However, an interesting phenomenon occurs inside nodes, where the opening and closing channels generates fluctuations that actually help to improve spike propagation itself. Considering the problem of parameter variations, the addition of noise in an excitable system based in RLC circuits and their influence in electrical spike transmission is explored.

- 2. Design and implementation of transistor-based digital circuits based on Stochastic Resonance. With reduction of power supply and threshold voltages following integrated circuit miniaturization, designs are more sensitive to parameter variations. One key parameter for correct performance of circuits, is threshold voltage. To show how stochastic resonance could be beneficial, we proposed the design of digital logic gates based on threshold logic. These circuits must have the following characteristics:

- Transistor-based design: currently the main element of integrated circuits is the transistor; therefore these circuits could be easily implemented into chip.

- Mismatch-tolerant designs : one of the main purposes is the design of circuits that work properly independently of parameter variations, such as threshold voltage, therefore, there is an intentional standard deviation introduced to the nominal value of threshold voltages among transistors.

- Low-power consumption.

- Stable output regardless introduction of noise: In the case of bistable systems assisted by noise, although noise is fundamental to generate transitions correlated with a weak input signal, there are fluctuations present at the output due to the presence of noise. in this case we propose a configuration with a stable output.

- 3. According to previous subsection, nanoscale MOS transistors and emerging devices exhibit also delays as well. Systems governed by single clock, like in the case of synchronous circuits, may have synchronization problems; therefore the study of different alternative to design delay-insensitive circuits should be explored. Therefore, asynchronous circuits are proposed as a good candidate. Study of such systems an their implementation is conducted as follows:

- Design of main elements to implement asynchronous circuits

- Exploration of the most optimal protocols according to our necessities

- Design and implementation of delay-insensitive, parameter-variation tolerant, low-power consumption circuits based on asynchronous design circuits as an application for noise-driven circuits.

Following the previous objectives, this thesis is outlined as follows:

Chapter 2 gives an introduction of the state of the art related with noisedriven phenomena in animal physiology, human perception system and brain. A brief description is provided along with examples suggesting that these biological structures have exploited noise through stochastic resonance phenomenon. Moreover, it is analyzed the effect of stochastic resonance in bistable systems is analyzed from the mathematical point of view, and it is shown how noise assists transition between two stable states. Additionally, a brief descriptions of the different types of stochastic resonance are provided and it is explained how they have been applied in engineering.

Chapter 3 presents the state of the art of noise-assisted spike transmission is presented, it is known that internal noise, mainly generated by the random opening and closing of ion channels, is the responsible for enhancing the response of spike transmission in the presence of conductance variations. In a deterministic model, spike transmission would be impossible if low conductance values are presented; however, internal fluctuations assist spike transition. In this chapter, FitzHugh-Nagumo is electrically modeled and its characteristics are studied. Here, an specific case of noise-assisted spike transmission is studied, where amplitude of noise is proportional to the amplitude of the spikes. The benefits of noise are demonstrated through circuit simulation.

Chapter 4 is focused on the circuit design of novel logic gates driven by noise (called SR logic gates). Based on threshold logic, a hysteresis differential amplifier is utilized to design logic gates that have three main advantages: parameter variation tolerance (threshold voltage variations), low-power consumption and stable response even in the presence of noise. It is demonstrated that the beneficial role of noise is a key factor to recover logic functions under the presence of threshold voltage variations. Moreover, the presence of stochastic resonance phenomenon is demonstrated mathematically. Simulation and experimental results are presented to evaluate the performance of the SR logic gates.

Chapter 5 presents possible applications of SR gates may be found in the field of asynchronous circuit design. SR gates has a dependence on stochastic processes and therefore their response exhibits a random delay. In the case of synchronous circuits, a central clock governs synchronization among stages, when delays are presented, synchronization problems may arise. One possible solution is the exploration of asynchronous circuits that offer many advantages over synchronous circuits: delay-insensitive circuits, lower power consumption and increase of processing speed; however this filed has nor been explored completely due to the lack of design and testing methodologies. Therefore this chapter offers a brief overview of basic theory of asynchronous circuits and concludes with the design of the basic elements of asynchronous circuits (based on the SR gates); it also includes design and circuit implementation of asynchronous pipelines (the backbone to design more complex asynchronous circuits) based on the SR logic gates. It is demonstrated through simulation and experimental results that delay-insensitive circuits based on the SR gates are achieved.

## References

- M. Horowitz, E. Alon, D. Patil, S. Naffziger, R. Kumar, and K. Bernstein "Scaling, power, and the future of CMOS," *Proceedings of IEEE International Electron Devices Meeting*, pp. 7-15, 2005

- [2] S. Nassif, N. Meht, and Y. Cao, "A resilience roadmap," *IEEE Design*, Automation & Test in Europe Conference (DATE), pp. 1011-1016, 2010

- [3] International Roadmap for Semiconductors, Semiconductor Industry Association(SIA), 2013, ed., Austin TX., Int. SEMATECH, 2013 [online]. Available at http://public.itrs.net

- [4] S. Saxena, C. Hess, H. Karbasi, A. Rossoni, S. Tonello, P. McNamara, S. Lucherini, S. Minehane, C. Dolainsky, and M. Quaratelli, "Variation in transistor performance and leakage in nanometer-scale technologies," *IEEE Transactions on Electron Devices*, vol. 55, no. 1, pp. 131-144, 2008.

- [5] R. Ho, K. Mai, and M. Horowitz, "The future of wires," Proceedings of the IEEE, vol. 89, no. 4, pp. 490-504, 2003.

- [6] A. Chaudhry, "Current challenges in scaling CMOS technology," Journal of Electrical & Electronics, vol. 1, no. 1, 2012.

- [7] Y. Kim, "Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics," *KIEEME Transactions on Electrical and Electronic Materials*, vol. 10, no. 1, pp. 93-105, 2010.

- [8] H. Iwai, "Roadmap for 22nm and beyond," *Microelectronic Engineering*, vol. 86, no. 7, pp. 1520-1528, 2009.

- [9] R.W. Brodersen, M.A. Horowitz, D. Markovic, B. Nikolic, and V. Stojanovic, "Methods for true power minimization," *IEEE/ACM International Confer*ence on Computer Aided Design, pp. 35-42, 2002

- [10] Samsung Electronics Co., Ltd., Analyst Day 2013, Available at http://www.dailytech.com

- [11] B. Lewin, T. Ytterdal, C. Wulff, and K. Martin "Analog Circuit Design in Nanoscale CMOS Technologies," *Proceedings of the IEEE*, vol. 97, no. 10, pp. 1687-1714, 2009.

- [12] W. Zhao, and Y. Cao "New generation of predictive technology model for sub-45nm design exploration," *Proceedings of the IEEE*, 7th International Symposium on Quality Electronic Design (ISQED), 2006.

- [13] V. Reddi, D. Pan, and K. Bowman, "Robust and resilient circuits from the bottom-up: technology, CAD, circuit, and system issues," *Proceedings of* the IEEE, 17th Asia and South Pacific on Design Automation Conference (ASP-DAC), pp. 7-16, 2012

- [14] T. Skotnicki, C. Fenouillet-beranger, C. Gallon, F. Boeuf, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, F. Arnaud, S. Clerc, M. Sellier, A. Cathignol, J.P Schoellkopf, E. Perea, R. Ferrant, and H. Mingam, "Innovative materials, devices, and CMOS technologies for low-power mobile multimedia," *IEEE Transactions on Electron Devices*, vol. 55, no. 1, pp. 96-130, 2008.

- [15] A. Hellemans, "Nanowire transistor could keep Moore's law alive," *IEEE Spectrum*, vol. 50, no. 5, pp. 14-16, 2013.

- [16] R. Marte, T. Schmidt, H.R. Shea, T. Hertel, and Ph. Avouris, "Single and multi-wall carbon nanotube field-effect transistors," *Applied Physics Letters*, vol. 73, no. 17, pp. 2447-2449, 1998.

- [17] M. Fujita, K. Wakabashi, K. Nakada, and K. Kusakabe, "Peculiar localized State at Zigzag Graphite Edge," *Journal of the Physical Society of Japan*, vol. 65, no. 7, pp. 1920-1923, 1998.

- [18] K.K. Likharev, K. Wakabashi, K. Nakada, and K. Kusakabe, "Single-elctron devices and their applications," *Proceedings of the IEEE*, vol. 89, no. 4, pp. 603-632, 1999.

- [19] M.R. Azghadi, O. Kavehei, and K. Navi, "A novel design for quantum-dot cellular automata cells and full adders," *Journal of Applied Sciences*, vol. 7, no. 22, pp. 3460-3468, 2012.

- [20] T. Skotnick, J. Hutchby, T. King, H.P. Wong, and F. Boeuf "The end of CMOS scaling: toward the introduction on new materials and structural changes to improve MOSFET performance," *IEEE Circuits and Devices Magazine*, vol. 21, no. 1, pp. 16-26, 2005.

- [21] S.G. Narendra, "Challenges and Design Choices in Nanoscale CMOS," ACM Journal on Emerging Technologies in Computing Systems (JETC), vol. 1, no. 1, pp. 7-49, 2005.

- [22] R. Daniel, J.R. Rubens, R. Sarpeshkar, and T.K. Lu, "Synthetic analog computation in living cells," *Nature*, vol. 497, pp. 619-623, 2013.

- [23] S. Mandal, and R. Sarpeshkar, "Circuit Models of Stochastic Genetic Networks," *Proceedings of the IEEE Biomedical Circuits and Systems Conference*, pp. 109-112, 2009.

- [24] A. Matsumoto, and Y. Miyahara, "Current and emerging challenges of field effect transistor based bio-sensing," *Nanoscale*, vol. 5, no. 22, pp. 10702-10718, 2013.

- [25] B.H. Calhoun, Y. Cao, X. Lin, K. Mai, L.T. Pileggi, R.A. Rutenbar and K.L. Shepard, "Digital circuit design challenges an opportunities in the era of nanoscale CMOS," *Proceedings of the IEEE (Special Issue on Integrated Electronics: Beyond Moore's Law)*, vol. 96, no. 2, pp. 343-365, 2008.

### Chapter 2

# Biological-inspired noise-driven phenomena and computing

### 2.1 Noise in nature

In this chapter, a brief review of the influence of fluctuations in biological systems is explored. Further, a formal definition of noise-driven phenomena is presented and some examples are provided. Following sections represent the theoretical basis for this thesis.

#### 2.1.1 Influence of noise on animal physiology

Nature inherently is a noisy environment, therefore many biological systems have learnt to adapt to such conditions. The first studies regarding how some biological structures use noise started with the study of the relationship between noise and and sensory neurons, since they are threshold systems that intrinsically generate noise [1]. There are other interesting studies, for example, the tail of a swimming predator, the crayfish possesses mechanoreceptors in its tail that are unable to detect weak signals without noise assistance [2]. In the same way, the sensory system of crickets can not detect weak signals coming from predators without assistance of environmental noise [3]. One of the latest experiments was conducted regarding the behavior of paddlefishes [4], that actually find its prey through emitted weak signals. It has been shown that, with the assistance of environmental noise, the paddlefish is able to find its prey faster rather than in the absence of noise (Fig. 2.1).

Previous examples show how noise-assisted tasks are exhibited at macrosclae

Figure 2.1: Examples of beneficial role of noise in animal kingdom: (a) cricket's hair, (b) crayfish and (c) paddlefish's sensory systems

biological systems. At cellular level SR effect has been also observed. It is speculated that SR effect has its origin in the ion channels of receptor cells membrane; it has been demonstrated through an artificial model that SR is exhibited [5]. The question that stills needs to be answered is whether SR is a phenomenon observed on a big scale level or it is also possible to be observed in a single ion channel. This result would have a great relevance, in fields as single-molecular devices.

#### 2.1.2 Influence of noise on human perception

• Human vision

An experiment was done consisting on a photo by adding noise with a

particular variance several times to create successive frames. This was done for different levels of noise variance, and a particularly optimal level was found for discerning the appearance of the image in the photo. Similar experiments also demonstrated an increased level of contrast sensitivity to sine wave gratings [6].

• Tactility

Human subjects who undergo mechanical stimulation of a fingertip are able to detect a subthreshold impulse signal in the presence of a noisy mechanical vibration. The percentage of correct detections of the presence of the signal was maximized for a particular value of noise [7].

• Audition

The auditory intensity detection thresholds of a number of human subjects were tested in the presence of noise. The subjects include four people with normal hearing, two with cochlear implants and one with an auditory brainstem implant [8]. The normal subjects were presented with two sound samples, one with a pure tone plus white noise and one with just white noise, and asked which one contained the pure tone. The level of noise which optimized the detection threshold in all four subjects was found to be between -15 and -20 dB relative to the pure tone, showing evidence of noise-assisted tasks in normal human hearing. A similar test in the subjects with cochlear implants only found improved detection thresholds for pure tones below 300 Hz, while improvements were found at frequencies greater than 60 Hz in the brainstem implant subject. The reason for the limited range of resonance effects are unknown. Additionally, the addition of noise to cochlear implant signals improved the threshold for frequency discrimination. In this work it is suggested that some type of white noise addition to cochlear implant signals could improve the utility of such devices.

#### 2.1.3 Influence of noise on human brain

There are many studies related with noise in the brain, these studies are mainly divided at physiological and higher cognitive levels.

At cognitive level, it has been shown that the relatively random spiking times of neurons could represent a source of noise that is involved in the generation of a probabilistic behavior that can prevent deadlock and facilitate for example, to decision-making processes [9]. Moreover, stochastic neurodynamical effects are

Figure 2.2: Necker cube, an example of a perceptual bistable process

important not only for decision-making processes, but also for memory recall, short-term memory, and attention.

Human brain does not work with deterministic computations, it is not a noiseless system but instead relies on stochastic dynamics. In the case of short term memory, spontaneous spikes can lead to a faster recovery of a memory. Another interesting case, is the perceptual decision-making, where perceptions can change spontaneously from one interpretation to another. A classical example is the Necker cube (Fig. 2.2), a perceptual bistable process, where two different states could be perceived. The hypothesis is that switching between multistable states is due to statical fluctuations on the network. This example provides an interesting demonstration on how noise can play a role for flipping from one attractor to another inside human brain. This experiment was already proved to be at [10], where an associative network with two stable states was trained so that both states have the same probability to be the perceived states; under the influence of a periodic weak force, SR effect is manifested.

There are another advantageous processes that arise due to the stochastic processes inside brain, just to mention some examples, creativity, where it has been speculated that without noise, the trajectory through a set of thoughts would tend to follow the same furrow each time, however under the influence of random spiking, these trajectories would be different each time, facilitating the creative thinking. More examples are found inside unpredictable behaviors, that represents an advantage when, for example, a prey is escaping from a predator.

### 2.2 Stochastic resonance

In this section, a formal definition of noise-driven phenomenon is presented.

#### 2.2.1 Definition

Stochastic resonance (SR) was first proposed to explain the periodic changes on glacial ages [11, 12]. It is known that climate processes are attained to several factors that generate variability. It was observed a periodicity of  $10^5$  years on ice ages and it was explained as a results of internal and external perturbations that affect earth climate and give rise to extreme climate changes. This phenomenon was called stochastic resonance and since then, there has been a great interest to study this phenomenon among physicists and mathematicians; therefore the definition of SR has been evolved during the last decades, but in general words it describes a phenomenon that involves the addition of an optimal amount of noise to a nonlinear system [13, 14], where its output quality is better than in the absence of noise, so it must be true that

*performance*(*noise* + *nonlinearsystem*) > *performance*(*nonlinearity*)

The classical graphical description of SR effect is depicted in Fig. 2.3, where the ball represents the state of a system trapped in a well of a double-well potential function; under the influence of a weak periodic signal, the ball would be trapped inside the well, however, under the influence of an external noise input, the ball could escape from one well to the other one. It has been shown that these escape events are not random, but there is correlation between the weak input signal and the escape rates. However, noise intensity should be tuned at its optimun, if the intensity of noise is increased, this correlation decreases; however too much noise could deteriorate the coherence of the output signal.

The term "stochastic resonance" was proposed because is involved with stochastic processes, and originally the graph signal-to-noise ratio was used as a performance measurement against noise intensity; the graph actually resembles the plot of frequency-dependent systems where there is a pick at a determined res-

Figure 2.3: Particle in a double-well potential under the influence of noise: (a) system in equilibrium, (b) system under the influence of a weak-periodic external signal (no transition), and (c) noise-assisted transition

onant frequency, thus the term "resonance" was used to name this phenomenon erroneously.

Further SR gained attention among biologist since it was discovered that some biological structures (including human brain), utilizes internal and external fluctuations to improve determined tasks [15, 16].

#### 2.2.2 Stochastic resonance in bistable systems

To understand the SR phenomenon, it is necessary to analyze it form the mathematical point of view. In the case of bistable systems, they posses an energy potential function with two minima (double-well potential function), which is represented in Fig. 2.3a. during equilibrium both wells have the same potential energy. However when an external force is introduced, the potential function of the wells is modified. If the external force is big enough, it may provoke a change on the current state. However, if this input has a low amplitude, it may not be enough to switch states (Fig. 2.3b); in this case, the introduction of a noisy input may assist these transitions (Fig. 2.3c).

Let's analyze a generic model of a overdamped motion of a Brownian particle in a bistable potential in the presence of noise and a periodic weak input, described

Figure 2.4: Noise-assisted transition in a double-well potential: (a) low intensity noise (b) optimal amount of noise (c) high amplitude noise

by:

$$x(t) = -V(x) + A\cos\omega_s t + \xi(t) \tag{2.1}$$

where A represents the amplitude of the period input signal and  $\xi(t)$  represents a zero-mean Gaussian white noise.

Here, the potential function is given by:

$$U(x) = -\frac{1}{2}x^2 + \frac{1}{4}x^4 \tag{2.2}$$

Where minimum points are found at U(x) = -1 and it has one saddle point at U(x) = 0.

To show the SR effect, the previous system was simulated using the Euler-Maruyama method. Fig. 2.4a shows the periodic input signal in the absence of noise. Fig. 2.4b shows the same system under the presence of noise. With the introduction of a low amplitude intensity noise, it may no be enough to excite the systems, however under the presence of an optimal amount of noise, a periodic response is observed. However, higher amplitude noise may provoke the system to be unstable (Fig. 2.4c).

There are many methods to evaluate the presence of SR phenomenon, but the classical method is through the graph SNR, where an optimal performance is observed at a certain amount of noise (Fig. 2.5).

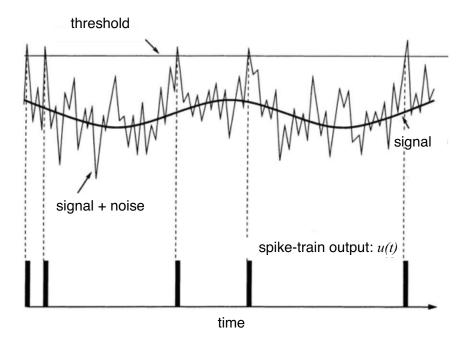

#### 2.2.3 Stochastic resonance in non-dynamical systems

The simplest system that shows SR effect consists of a non-dynamical system with a threshold and a periodic weak signal as input [17]. Without noise this signal will never cross the threshold, however when noise is introduced a series of spike-like output signals are generated (Fig. 2.6).

#### 2.2.4 Suprathreshold stochastic resonance

This is a special type of SR, and it happens where there is a set of excitable circuits sharing same input x [18]. These systems have the characteristic of having one threshold  $\theta$ . In this case, independent white noise sources  $\eta_N(t)$ are applied individually to each circuit, enhancing their response y (Fig. 2.7). Usually the performance measurement is given by the typical measurements of mutual information.

Figure 2.5: Characteristic curve Signal to Noise Ratio (SNR) exhibiting SR

Figure 2.6: Non-dynamical SR

#### 2.2.5 Applications of stochastic resonance

SR effect also gained attention in engineering field. In the case of electrical engineering, noise always has been considered as a signal with negative effects and

Figure 2.7: Suprathreshold SR system

thus the idea of a positive utilization of noise seems counterintuitive. However there have been a lot of studies related with SR effect and its applications in engineering. Just to mention the most remarkable applications in the field of biomedical engineering: Suprathreshold stochastic resonance was applied to the improvement of cochlear implants, the quality of these implants is still not optimal, and patients are still unable to distinguish sounds in noisy environments as well as distinguish musical instruments inside a pice of classical music. The idea here is that such artificial implants lack natural sensory hair cells that are used by human ear to encode sounds. These organelles posses inherent randomness, so the idea here is that with the introduction of artificial noise in artificial cochleas may help to improve hearing [19]. SR also found applications in the improvement of life-supported ventilators, where additional noise may be positive to emulate natural fluctuations in the respiratory system [20]. Moreover, SR effect has been used for improving the tactile sensation for patients having underthreshold tactile sensitivity [21]. Another application is found in the baroreflex, where a negative feedback is the responsible for controling blood pressure, by decreasing or increasing the heart rate; this compensation was found to be optimized by the addition of noise to arterial blood pressure receptor [22]. Balance control in patients with diabetes or affected by a stroke, can be also optimized through the use of noise [23, 24].

Also, the phenomenon of SR has been also observed at bistable devices, such as tunnel diodes [25], optical systems, as in the case ring lasers [26] and magnetic systems [27]. Quantum phenomena also have been studied [28] and climate phenomenon and social-ill models [29, 30]. At electrical system level, SR has application in image filtering derived by the theory of non-dynamical SR; also it has been demonstrated to play a role on circuit synchronization, where the introduction of noise enhance synchronization on a network of oscillators [31]. Suprathreshold SR has applications in the design of analog to digital converters [32], as well as in the design of low-power digital accelerometers [33] and delta-sigma modulators [34]. At device level, SR has been observed at molecular devices [35].

# References

- P. Hanggi, "Stochastic resonance in biology how noise can enhance detection of weak signals and help improve biological information processing," *Chemphyschem*, vol. 3, pp. 285-290, 2002.

- [2] J.K. Douglas, L. Wilkens, E. Pantazelou, and F. Moss "Noise enhancement of information transfer in crayfish mechanoreceptors by stochastic resonance," *Nature*, vol. 365, pp. 337-340, 1993.

- [3] J.E. Levin, and J.P. Miller "Broadband neural encoding in the cricket ceral sensory systems enhanced by stochastic resonance," *Nature*, vol. 380, pp. 165-168, 1996.

- [4] D.F. Russell, L.A. Wilkes, and F. Moss "Use of behavioral stochastic resonance by paddle fish for feeding," *Nature*, vol. 402, pp. 291-294, 1999.

- [5] H.Y. Li, J. Ma, Z.H. Hou, and H.W. Xin, "Constructive role of internal noise for the detection of weak signal in cell system," *Acta Physico-Chimica Sinica*, vol. 24, no. 12, pp. 2203-2206, 2008.

- [6] E. Simonotto, M. Riani, C. Seife, M. Roberts, J. Twitty, F. Moss, "Visual perception of stochastic resonance," *Physical Review Letters*, vol. 78, no. 6, pp. 1186-1189, 1997.

- [7] J. Collins, and P. Grigg, "Noise enhance tactile sensation," *Nature*, vol. 383, no. 31, p. 770, 1996.

- [8] F. Zeng, Q. Fu, and R. Morse "Human hearing enhanced by noise," Brain Research, vol. 896, pp. 251-255, 2000.

- [9] E.T. Rolls, G. Decco, The noisy brain, stochastic dynamics as a principle of brain function, Oxford University Press, 2010.

- [10] M. Riani, E. Simonotto, "Periodioc perturbation of ambiguous figure: a neural network model and non-simulated experiment," *IL NUOVO CIMENTO*, vol. 17, pp. 903-913, 1995.

- [11] R. Benzi, Parisi G., Sutera A., Vulpiani A., "Stochastic resonance in climate change," *Tellus*, vol. 34, pp. 10-16, 1982.

- [12] R. Benzi, "Stochastic resonance: from climate to biology," Nonlinear Processes in Geophysics, vol. 17, pp. 431-441, 2010.

- [13] L. Gammaitoni, P. Hanggi, P. Jung, and F. Marchesoni, "Stochastic resonance," *Reviews of Modern Physics*, vol. 70, no. 3, pp. 223-287, 1998.

- [14] M.D. McDonell, and D. Abbott, "What is stochastic resonance? Definitions, misconceptions, debates, and its relevance to biology," *PLoS Computational Biology*, vol. 5, no. 5, pp. 1-9, 2009.

- [15] A. Faisal, L.P.J. Selen, and D.M. Wolpert, "Noise in the nervous system," *Nature Reviews Neuroscience*, vol. 9, no. 4, pp. 292-303, 2008.

- [16] S. M. Bezrukov, I. Vodyanoy, "Noise-induce enhancement of signal transduction across voltage dependent ion channels" *Nature*, vol. 378, no. 6555, pp. 362-364, 1995.

- [17] Z. Gingl, L.B. Kiss, F. Moss, "Non-dynamical stochastic resonance: theory and experiments with white and arbitrary colored noise," *Europhysics Letters*, vol. 29, no. 3, pp. 191-196, 1995.

- [18] Y. Guo, and J. Tan, "Suprathreshold stochastic resonance in multilevel threshold system driven by multiplicative and additive noise," *Communications in Nonlinear Science and Numerical Simulation*, vol. 18, no. 10, pp. 2852-2858, 2013.

- [19] M. Chatterjee, and M.E. Robert "Noise enhances modulation in cochlear implant listeners: stochastic resonance in a prosthetic sensory system?," *Journal of the Association for Research in Otolaryngology*, vol. 2, pp. 159-171, 2001.

- [20] B. Suki, A.M. Alencar, M.K. Sujeer, K.R. Lutchen, J.J. Collins, J.S. Andrade, E.P. Ingenito, S. Zapper, and H.E. Stanley "Life-support systems benefits from noise," *Nature*, vol. 393, pp. 127-128, 1998.

- [21] K. Beceren, M. Ohka, T. Jin, T. Miyaoka, and H. Yussof "Optimization of tactile sensation using stochastic resonance," *Proceedia Engineering*, vol. 41, pp. 792-797, 2012.

- [22] I. Hidaka, D. Nozaki, Y. Yamamoto, "Functional Stochastic resonance in the human train: noise induced sensitization of barolex systems," *Physical Review Letters*, vol. 85, no. 17, pp. 3740-3743, 2000.

- [23] A.A. Priplata, B.L. Patritti, J.B. Niemi, R. Hughes, D.C. Gravelle, L.A. Lipsitz, A. Veves, J. Stein, P. Bonato, and J.J. Collins "Noise-enhanced balance control in patients with diabetics and patiences with stroke," *Annals Neurology*, vol. 59, pp. 4-12, 2006.

- [24] F. Moss, J.G. Milton "Balancing the unbalanced," Nature, vol. 425, pp. 911-912, 2003.

- [25] R.N. Matenga, B. Spagnolo, "Stochastic resonance in a tunnel diode in the presence of white and colored noise," *IL NUOVO CIMENTO*, vol. 17, no. 7-8, pp. 873-881, 1995.

- [26] B. McNamara, K. Wiesenfeld, R. roy, "Observation of stochastic resonance in a ring laser," *Physical Review Letters*, vol. 60, no. 25, pp. 2626-2629, 1988.

- [27] A.N. Grigorenko, P.I. Nikitin, G.V. Roshchepkin, "Observation of stochastic resonance in a monostable magnetic system," *Journal of Experimental and Theoretical Physics Letters*, vol. 65, no. 10, pp. 828-832, 1997.

- [28] R. Lofstedt, and S.N. Coppersmith, "Quantum stochastic resonance," *Phys-ical Review Letters*, vol. 72, no. 13, pp. 1947-1950, 1994.

- [29] L. Stone, P. Saparin, A.A. Huppert, C. Price, "El Nino chaos: the role of noise and stochastic resonance on the enso cycle" *Geophysical Research Letters*, vol. 25, pp. 175-178, 1998.

- [30] R. Wallace, D. Wallace, H. Andrews, "Aids, tuberculosis, violent crime, and low birthweight in eight us metropolitan areas: public policy, stochastic resonance, and the regional diffusion of inner-city markers," *Environmental* and Planning A, vol. 29, pp. 525-555, 1997.

- [31] L.M. Ward, S. MscLean, and A. Kirshner, "Stochastic resonance modulates synchronization with and between cortical sources," *PLOS ONE*, vol. 5, p. e14371, 2010.

- [32] M.D. Mc.Donell, N.G. Stocks, C.E.M. Pearce, and D. Abbott "Analog to digital conversion using suprathreshold stochastic resonance," *Proceedings* of SPIE, vol. 5649, pp. 75-84, 2005.

- [33] R.H. Oisson, D.W Carr, "A digital accelerometer array utilizing suprathreshold stochastic resonance for detection of aub-browinian noise floor acceleration," *Sandia Report*, 2004.

- [34] O. Oliaeu, "Stochastic resonance in sigma-delta modulators," *Electronics Letters*, vol. 39, no. 2, pp. 173-174, 2003.

- [35] Y. Hirano, Y. Segawa, T. kawai, T. Matsumoto, "Stochastic resonance in a molecular redox circuit," *Physical Chemistry C*, vol. 117, pp. 140-145, 2013.

## Chapter 3

# Spike transmission assisted by noise

## 3.1 Biological background: spike transmission in nervous system

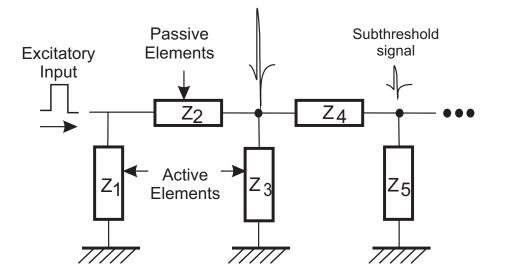

As an example of noise assisted tasks, we can find the improvement of the ability to detect weak signals in biological systems [1-5]. Several studies have demonstrated that the nervous system contains several sources of noise and research in this field has demonstrated that the nervous system has adopted these noise sources to improve its efficiency as it was reviewed in the previous chapter. Following this background, this chapter is based on the study of the technique used by myelinated axons to transmit spikes [6], based on the stochastic resonance (SR) effect. This is in order to emulate its dynamics to assist weak signal propagation in transmission lines with high values of internodal resistors. Correct information transmission is a key factor in active transmission lines [7]. An active transmission line in non-uniform medium is modeled as a chain of connected active compartments (Fig. 3.1), which are connected each other through resistive impedances (internodal resistances). The value of internodal resistances can fluctuate and sometimes acquire high values, provoking a loss of information. The influence of independent noise on improving spike transmission in nervous system, has been already investigated [8–13].

However, there is a characteristic that have not yet taken on account and it is the role of dynamic noise. Therefore, the main point of this section is to consider the dependence of noise on the membrane potential amplitude, where a similar electrical model of a transmission line is found in myelinated axons. This characteristic allows a proper spike transmission, discriminating weak signals from parasitic fluctuations, that could generate a fake response. Inspired by this idea, we investigate how noise enhances the performance of spike transmission in serially-connected electrically circuits receiving subthreshold inputs.

Exploring how these biological structures are able to transmit information even in the presence of low conductances, may help to improve information transmission in electrical systems, having as a main point of this chapter, exploiting dynamical noise on spike transmission.

Figure 3.1: Basic model of transmission line in non-uniform medium.

The following section will review briefly the biological background of spike transmission as well as the theory of excitable models (used to emulate biological spike transmission).

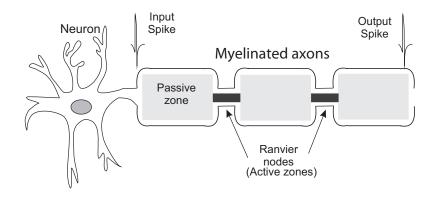

#### 3.2 Excitable models

Excitable systems are observed in a wide range of natural systems and they can be defined as monostable systems, where if the system is unperturbed, it will remain in the rest state, but once it is triggered by a strong perturbation, the system is moved to an excited state (or firing). In the nervous system, myelinated axons serve to transmit spikes in an excitable medium. Myelinated axons represent a very efficient biological technique to transmit spikes along large axons. This kind of axons are divided into segments separated each other through high-density ion channel regions, known as the Ranvier nodes (Fig. 3.2), which actually can be modeled electrically as active components. On the other hand, low-density ion channel segments can be modeled as passive components. In that way, a myelinated axon is electrically represented as active elements connected each other through passive segments. A fact about myelinated axons is that the internodal resistances associated to the low density ion channel regions, are not the same for every segment (mainly due to variations on dimensions along the axon), so that in the same axon, we can find segments that possess a high resistivity, as well as segments with low resistivity. In the case of high resistivity segments, spike transmission is stopped. However, it has been demonstrated that although high resistance values exist, spike transmission is successful; so the question is how this biological design is able to transmit spikes successfully? The answer comes from the intrinsic noise generated by the opening and closing ion channels inside the Ranvier nodes. This uncorrelated noise, contributes with the improvement of spike transmission rate. Information transmission with noise assistance has been extensively studied in bistable systems and in electrical systems.

Figure 3.2: General scheme of myelinated axons.

However, previous works have considered noise sources as independent sources. In this chapter, it is introduced the effect of dynamical noise on system response. Experimental results from pyramidal neurons from rat neocortex, show the intrinsic noise has a non-linear dependence on membrane potential [14]. Steinmetz et al., using the classical Hodgkin and Huxley model, predict that the standard deviation of voltage noise increases as the membrane potential is depolarized; the cause of this increment, is the increase of the probability that ion channels open [15]. We will further introduce the importance of including membrane potential dependent noise for correct spike transmission in our current model.

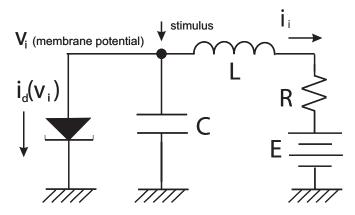

#### 3.2.1 FitzHugh-Nagumo model

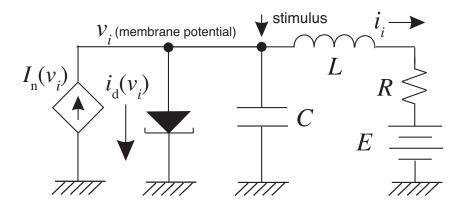

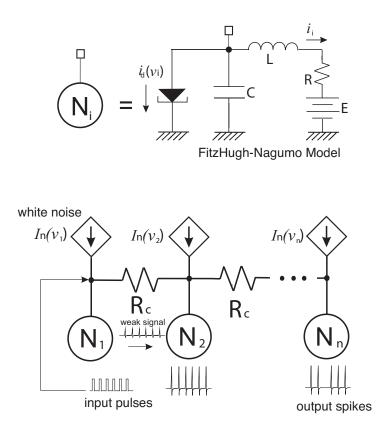

Figure 3.3: FitzHugh-Nagumo circuit.

It is employed an electrical circuit of the FitzHugh-Nagumo model operating in the excitable mode [16] to emulate myelinated axons. FitzHugh-Nagumo model has been widely used to emulate conductance-based neuron models as a simplification of Hodgkin-Huxley model, having cubic nullclines, where its dynamical behavior is represented by the following system of differential equations:

$$\frac{dV}{dt} = f(V) - W + I \tag{3.1}$$

$$\frac{dW}{dt} = a(bV - cW) \tag{3.2}$$

Where f(V) is given by a cubic function of the form  $V - V^3$ . The nullclines of the FitzHugh-Nagumo model have a cubic and a linear form given by:

$$\frac{dV}{dt} = 0 \to \quad W = f(V) + i \quad \text{(V-nullcline)}$$

(3.3)

$$\frac{dW}{dt} = 0 \to \quad W = \left(\frac{b}{c}\right) V \quad (W-nullcline) \tag{3.4}$$

These nullclines can intersect in one, two or three points, resulting in one, two, or three equilibria, all of which may be unstable. There is an electrical circuit that possesses the same dynamic of the FitzHugh-Nagumo model and is shown in Fig. 3.3.

The dynamical equations governing the circuit from Fig. 3.3 are given as follows:

$$C\frac{dv}{dt} = i - i_d(v) \tag{3.5}$$

$$L\frac{di}{dt} = E - Ri - v \tag{3.6}$$

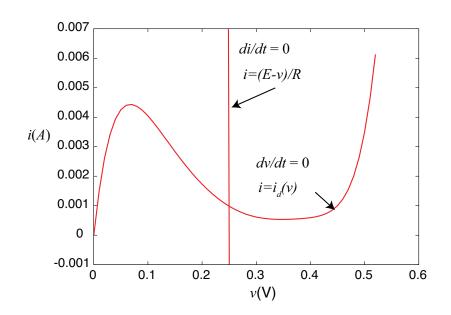

Where  $i_d(v)$  represents the characteristic curve of a tunnel diode and could be described as a cubic function (Fig. 3.4) and v-nullcline and *i*-nullcline (Fig. 3.5) are given by:

$$\frac{dv}{dt} = 0 \rightarrow \quad i = i_d(v) \quad \text{(v-nullcline)}$$

$$\frac{di}{dt} = 0 \rightarrow \quad i = \frac{(E-v)}{R} \quad \text{(i-nullcline)}$$

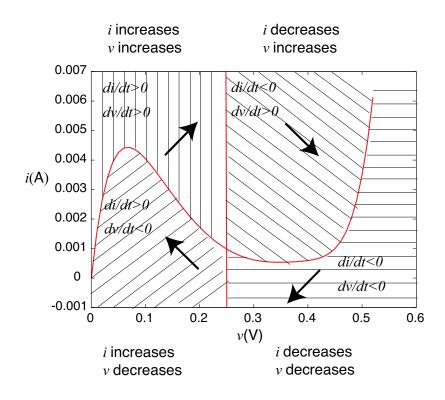

Figure 3.6 depicts the v-nullcline and i-nullclines and their difference areas.

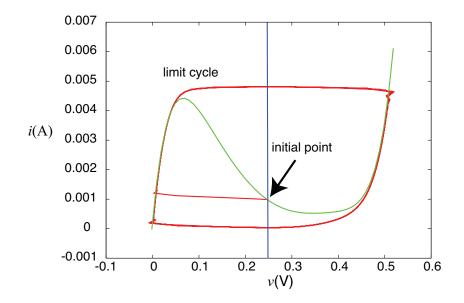

In order to demonstrate the previous model, simulations were performed using the following parameters: E=0.25V,  $L=10 \ \mu H$ , C=100pF, and  $R = 0.2\Omega$ , where under these parameters, the system will have a limit cycle around the fixed point (Fig. 3.7) [17], and the membrane potential behaves as a spike train (Fig. 3.8).

In order to establish a formal analysis for the fixed points of this system, the eigenvalues are obtained for a linear part of the v-nullcline. Then, we have the following matrix representation:

$$\begin{pmatrix} \frac{dv}{dt} \\ \frac{di}{dt} \end{pmatrix} = \begin{pmatrix} -\frac{g}{C} & \frac{1}{C} \\ -\frac{1}{L} & -\frac{R}{L} \end{pmatrix} \begin{pmatrix} v \\ i \end{pmatrix} + \begin{pmatrix} -\frac{q}{C} \\ \frac{E}{L} \end{pmatrix}$$

(3.7)

Figure 3.4: Plot of the i-v characteristic of the diode utilized to simulate the FitzHugh-Nagumo circuit, where clearly a cubic function is observed

where  $i_d(v) = gv + q$  with  $g = -10e^3$  and  $q = 3.5e^3$ ; and the fixed points are given by  $(v^*, i^*) = \left(\frac{E - qR}{Rg + 1}, \frac{q + gE}{Rg + 1}\right)$ . If  $V = v - v^*$  and  $I = i - i^*$ , therefore we have:

$$\begin{pmatrix} \frac{dV}{dt} \\ \frac{dI}{dt} \end{pmatrix} = \begin{pmatrix} -\frac{g}{C} & \frac{1}{C} \\ -\frac{1}{L} & -\frac{R}{L} \end{pmatrix} \begin{pmatrix} V \\ I \end{pmatrix}$$

(3.8)

Here the stability can be determined through the eigenvalues of the systems:

$$\begin{pmatrix} \frac{dV}{dt} \\ \frac{dI}{dt} \end{pmatrix} = \begin{pmatrix} a & b \\ c & d \end{pmatrix} \begin{pmatrix} x \\ y \end{pmatrix}$$

,

Figure 3.5: v-nullcline and *i*-nullcline for the circuit of Fig. 3.3

$$\begin{pmatrix} a - \lambda & b \\ c & d - \lambda \end{pmatrix}$$

The eigenvalues are given by  $\lambda = \frac{(a+b) \pm \sqrt{(a+d)^2 - 4(ad-bc)}}{2}$ . From the equation system 3.8,  $a = -\frac{g}{C}$ ,  $b = \frac{1}{C}$ ,  $c = -\frac{1}{L}$ , and  $d = -\frac{R}{L}$ . Therefore, the eigenvalues for our systems are given by:

$$2\lambda = -\left(\frac{g}{C} + \frac{R}{L}\right) \pm \sqrt{\left(\frac{g}{C} + \frac{R}{L}\right)^2 - 4\frac{1+gR}{CL}}$$

(3.9)

If  $\lambda > 0$ , the response increases exponentially; if  $\lambda < 0$  the system converge to a stable point; and if  $\lambda$  is complex, then the system is oscillatory. Therefore, to determine when the system is stable,  $\lambda$  should be negative. To obtain this result, it should be true that  $-g > \sqrt{\frac{C}{L}}$ . Evidently,  $\sqrt{\frac{C}{L}}$  must be complex, which is impossible in terms of physical devices. However, if E is reduced to

Figure 3.6: Four different areas are shown, according to the fixed point of v-nullcline and *i*-nullcline, where the direction of the vector field depends on the regions

0.05V, then the new linear region of v-nullcline has  $g = 20e^{-3}$ , with this value it is possible to have an stable fixed point, since the condition  $\lambda < 0$  is true. Electrical simulation were performed, and it can be shown that parametric plot *i* versus v has a trajectory that converges to the sable fixed point (Fig. 3.9); also the temporal plot of membrane potential is shown in Fig. 3.10.

Figure 3.7: Parametric plot of i versus the membrane potential v, where clearly its trajectory is represented by a limit cycle, according to the circuit parameters

Figure 3.8: Spike-like membrane potential v

Figure 3.9: Parametric plot of i versus the membrane potential v, where the new fixed point is stable

Figure 3.10: Spike-like membrane potential, after firing, the state returns to an stable state  $\boldsymbol{v}$

## 3.3 Noise-assisted spike transmission along excitable circuits

In this section, circuit design and electrical simulations are performed for noiseassisted spike transmission along a chain of excitable circuits (FitzHugh-Nagumo).

#### 3.3.1 Circuit design

To emulate the noise effect in spike transmission, a current noise source in parallel with a tunnel diode was embedded (Fig. 3.11).

Figure 3.11: Noise-driven FitzHugh-Nagumo circuit.

On the other hand, if we consider a chain of electrical circuits, connected to each other by resistors  $R_c$ , the *n*-th circuit is described using the discrete FitzHugh-Nagumo equations as:

$$C\frac{dv_n(t)}{dt} = I_n(t) - i_{d,n}(t) + \frac{v_{n-1}(t) + v_{n+1}(t) - 2v_n}{R_c}$$

(3.10)

$$L\frac{di_n(t)}{dt} = E - R \cdot I_n(t) - v(t)$$

(3.11)

where  $R_c$  represents the internodal resistance.

Figure 3.12: Block diagram of serially-connected circuits with noise-assisted spike propagation

The dynamics of the 1-D excitable medium (our virtual axon), where the excitable circuits were locally coupled, are represented by the continuous forms given by Eq. 3.12 and Eq. 3.13:

$$C\frac{\partial v(x)}{\partial t} = g\frac{\partial^2 v(x)}{\partial x^2} + i(x) - i_{\rm d}[v(x)] + I_{\rm n}[v(x)]$$

(3.12)

$$L\frac{\partial i(x)}{\partial t} = E - R \cdot i(x) - v(x)$$

(3.13)

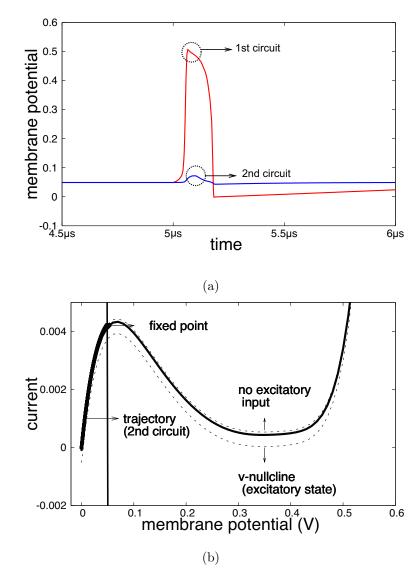

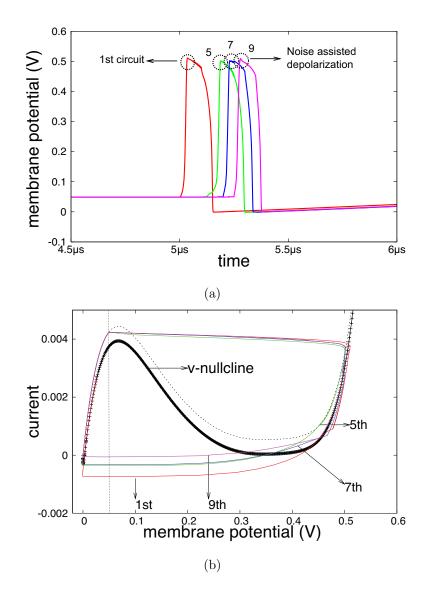

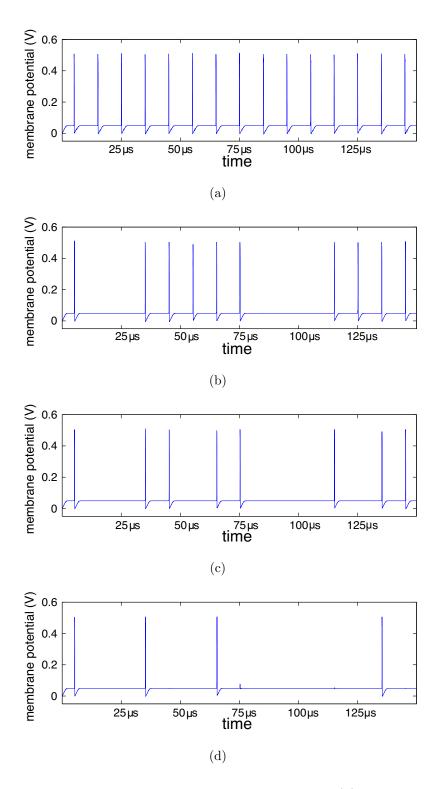

where x represents the space,  $i_d(\cdot)$  the *i*-v characteristics of the tunnel diode, v(x) the membrane potential at x, E the resting potential, and  $I_n[v(x)]$  the v(x)dependent dynamic noise current where the noise current is generated only when v > E.