# A Study on Acceleration Methods of Data Center Applications with Reconfigurable Hardware

Eric Shun Fukuda

A thesis presented for the degree of Doctor of Engineering

Graduate School of Information Science and Technology Hokkaido University Japan March, 2015

## A Study on Acceleration Methods of Data Center Applications with Reconfigurable Hardware

### Eric Shun Fukuda

### Abstract

This study discusses the use of reconfigurable hardware, especially in data centers. Reconfigurable hardware is a promising technology for overcoming the difficulties face by general-purpose processors, which have been central to computer science for decades. Enabling reconfigurable technology to be used by a variety of people, including software developers, will have a great impact on pushing current computing to a new era. The recent enthusiasm for cloud computing indicates the increasing significance of data centers, and improving the performance of data centers in computation speed and energy efficiency has a great impact on the entire computer industry.

Although computers have progressed enormously since their invention, physical restriction is beginning to prevent them from achieving higher computation speed and energy efficiency. These two matrices, computation speed and energy efficiency, are critical in data centers that handle gigantic data traffic from all over the world. As the amount of data that data centers handle is growing even more, computer developers need different ways of improving computers. Among the several alternatives that have been proposed, reconfigurable hardware is one of the most suitable choices, and this is what we try to use in this study. Reconfigurable hardware promises higher performance and energy efficiency in many application domains, and several research groups have been trying to deploy it in data centers.

Meanwhile, reconfigurable hardware is used mainly by embedded or networking device vendors, and curious end users often simply enjoy trying them with reconfigurable boards purchased on their own. This is because it is difficult to obtain higher performance with inexpensive reconfigurable boards, which an individual can buy, than with a commercially available general-purpose processor, and reconfigurable boards that can exceed the performance of commercial general-purpose processor are too expensive for end users to buy individually. By deploying reconfigurable hardware and making it available to the public, the cost of utilizing reconfigurable hardware will go down and thus more end-users will be eager to use it. More applications such as databases that require very low latency will be built on reconfigurable hardware as well as general-purpose processors. Such a computing system, which uses several general-purpose processors and reconfigurable devices or heterogeneous systems, is too complicated for end users' everyday use. As a consequence, to make the system look simple for the end users, it will become more transparent: they will eventually not notice which kind of computing device they are using.

However, there are many problems that must be solved before such a cloud system can be widely used. Among them, we focus on two major problems in this study: developing applications with reconfigurable hardware is more difficult compared to software applications, thus, the cost of developing the application is higher; and a method for using reconfigurable hardware in data centers is not established.

In order to solve the first problem, we assess where the difficulties lie in the state of the art design method that uses high-level synthesis tools for developing hardware accelerated application systems, and propose a method to overcome the difficulties. For solving the other problem, we propose a new technique of using reconfigurable hardware in data centers.

## Contents

| 1        | Intr | oduction                                                                                                                                                         | <b>7</b> |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | 1.1  | Background                                                                                                                                                       | 7        |

|          |      | 1.1.1 Problems of General Purpose Processors                                                                                                                     | 7        |

|          |      | 1.1.2 Applications on Hardware                                                                                                                                   | 8        |

|          |      | 1.1.3 Growing Popularity of Reconfigurable Hardware                                                                                                              | 9        |

|          |      | 1.1.4 Reconfigurable Hardware in Data Centers                                                                                                                    | 11       |

|          |      | 1.1.5 Open Issues of Reconfigurable Hardware in Data Centers                                                                                                     | 13       |

|          |      | 1.1.6 Future of Reconfigurable Hardware in Data Centers $\Box$                                                                                                   | 18       |

|          | 1.2  | Organization                                                                                                                                                     | 20       |

|          | Refe | rences                                                                                                                                                           | 22       |

| <b>2</b> | Acc  | eleration by HLS 2                                                                                                                                               | 24       |

|          | 2.1  | Introduction                                                                                                                                                     | 24       |

|          | 2.2  | Stream Processing                                                                                                                                                | 25       |

|          | 2.3  | Related Work                                                                                                                                                     | 26       |

|          | 2.4  | DRP: The Evaluation Platform                                                                                                                                     | 28       |

|          | 2.5  | Window Join on DRP                                                                                                                                               | 29       |

|          |      | 2.5.1 Evaluation Strategy $\ldots \ldots \ldots$ | 30       |

|          |      | 2.5.2 Step 1: Pure Software Code                                                                                                                                 | 31       |

|          |      | 2.5.3 Step 2: Sliding Window Buffer                                                                                                                              | 32       |

|          |      | 2.5.4 Step 3: Parallel Output Buffer                                                                                                                             | 33       |

|          |      | 2.5.5 Step 4: Match Table                                                                                                                                        | 35       |

|          |      | 2.5.6 Step 5: Chunk Data Prefetching                                                                                                                             | 36       |

|          |      | 2.5.7 Step 6: Parallel Table Lookup                                                                                                                              | 37       |

|          |      | 2.5.8 Step 7: Loop Folding (Pipelining)                                                                                                                          | 38       |

|   |      | 2.5.9 Step 8: Low Match Rate Optimization                                                                                      |

|---|------|--------------------------------------------------------------------------------------------------------------------------------|

|   | 2.6  | Discussion                                                                                                                     |

|   |      | 2.6.1 Optimization Overview                                                                                                    |

|   |      | 2.6.2 Performance                                                                                                              |

|   |      | 2.6.3 Lessons learned $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 46$                                      |

|   |      | 2.6.4 Adaptive Stream Processing                                                                                               |

|   | 2.7  | Summary                                                                                                                        |

|   | Refe | erences                                                                                                                        |

| 3 | Acc  | eleration by a Hybrid Approach of HLS and RTL 53                                                                               |

|   | 3.1  | Introduction                                                                                                                   |

|   | 3.2  | Related Work                                                                                                                   |

|   | 3.3  | SQL-Based Stream Processing Language                                                                                           |

|   | 3.4  | Our Approach                                                                                                                   |

|   |      | 3.4.1 Generalization of Queries into Abstract Hardware 58                                                                      |

|   |      | 3.4.2 Mapping Abstract Hardware to C Code                                                                                      |

|   |      | 3.4.3 Shallow Hardware Optimization in C Code                                                                                  |

|   | 3.5  | $Evaluation \dots \dots$ |

|   | 3.6  | Discussion                                                                                                                     |

|   | 3.7  | Conclusion                                                                                                                     |

|   | Refe | erences                                                                                                                        |

| 4 | Acc  | celeration by I/O Caching 69                                                                                                   |

| _ | 4.1  | Introduction                                                                                                                   |

|   | 4.2  | Key-value Stores in Data Centers                                                                                               |

|   | 4.3  | Background                                                                                                                     |

|   |      | 4.3.1 Memcached                                                                                                                |

|   |      | 4.3.2 Related Work                                                                                                             |

|   | 4.4  | Concept of NIC Cache                                                                                                           |

|   | 4.5  | Cache Simulation                                                                                                               |

|   | -    | 4.5.1 Testing Tool                                                                                                             |

|   |      | 4.5.2 Simulation Results                                                                                                       |

|   | 4.6  | Hardware Design                                                                                                                |

|   | -    | 4.6.1 Experimental Conditions                                                                                                  |

|   |      | 1                                                                                                                              |

|                      |      | 4.6.2  | Latency  |          |      |   |       |     |     |   |  |   |  |   |   |  |   | 89 |

|----------------------|------|--------|----------|----------|------|---|-------|-----|-----|---|--|---|--|---|---|--|---|----|

|                      |      | 4.6.3  | Through  | put      |      |   |       |     |     |   |  |   |  |   |   |  |   | 90 |

|                      | 4.7  | Cache  | Size Max | imizatic | on   | • |       |     |     |   |  |   |  | • | • |  |   | 90 |

|                      | 4.8  | Discus | sion and | Future V | Work | • |       |     |     |   |  |   |  |   |   |  |   | 94 |

|                      | 4.9  | Conclu | usion    |          |      |   | <br>• |     |     |   |  |   |  | • |   |  |   | 95 |

|                      | Refe | rences |          |          |      | • | <br>• | •   |     | • |  | • |  | • |   |  | • | 96 |

| <b>5</b>             | Con  | clusio | n        |          |      |   |       |     |     |   |  |   |  |   |   |  |   | 98 |

| Acknowledgement      |      |        |          |          |      |   | 1     | .03 |     |   |  |   |  |   |   |  |   |    |

| List of Publications |      |        |          |          |      |   |       | 1   | .04 |   |  |   |  |   |   |  |   |    |

# List of Figures

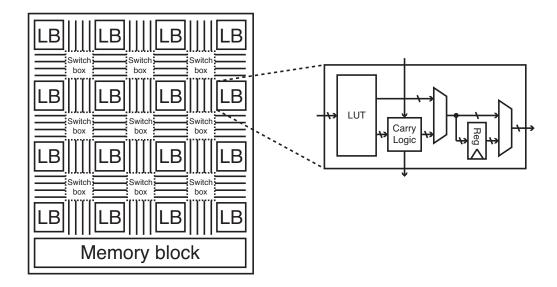

| 1.1  | Simplified architecture of a typical reconfigurable hardware. $% \left( {{{\bf{x}}_{{\rm{s}}}}} \right)$ . | 9  |

|------|------------------------------------------------------------------------------------------------------------|----|

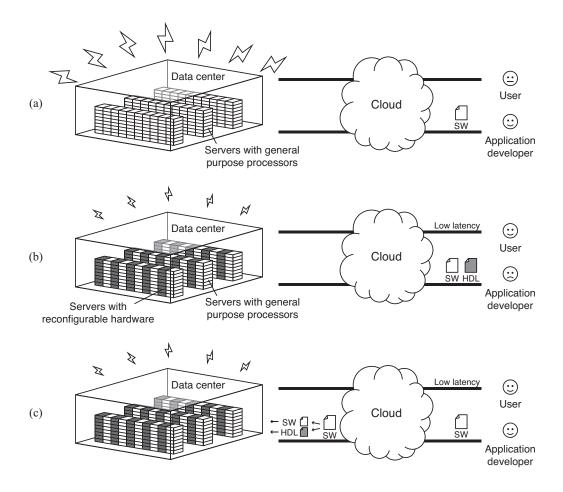

| 1.2  | Replacing general purpose processors in data centers with re-                                              |    |

|      | configurable hardware.                                                                                     | 11 |

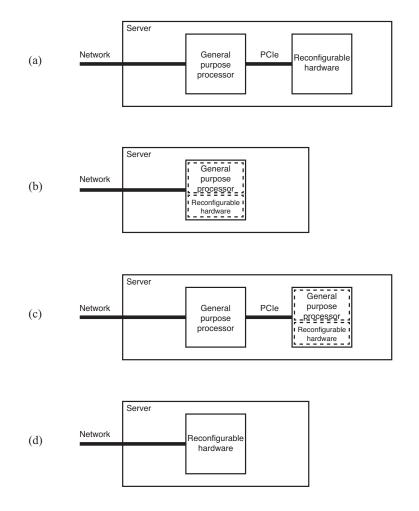

| 1.3  | Variations of organization of servers with reconfigurable hard-                                            |    |

|      | ware                                                                                                       | 15 |

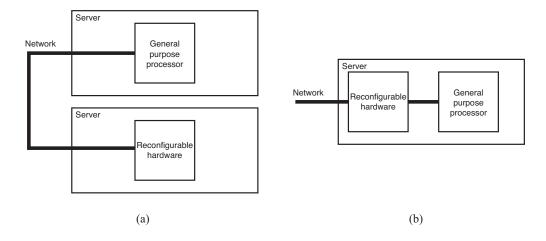

| 1.4  | Two architectures of servers for reconfigurable hardware and                                               |    |

|      | general purpose processors.                                                                                | 17 |

| 2.1  | Compilation flow.                                                                                          | 27 |

| 2.2  | DRP hardware overview.                                                                                     | 28 |

| 2.3  | Join and window join. $\ldots$                                                                             | 30 |

| 2.4  | Synthesized hardware (Step 1)                                                                              | 32 |

| 2.5  | Synthesized hardware (Step 2).                                                                             | 34 |

| 2.6  | Expected hardware (Step 3).                                                                                | 36 |

| 2.7  | Synthesized hardware (Step 4).                                                                             | 38 |

| 2.8  | Timing chart of the folding.                                                                               | 39 |

| 2.9  | Synthesized hardware (Step 8).                                                                             | 41 |

| 2.10 | Throughput improvement.                                                                                    | 45 |

| 2.11 | Match rate dependency (Step 7 vs 8)                                                                        | 48 |

| 3.1  | Comparison of conventional and our approaches.                                                             | 55 |

| 3.2  | Example queries and schema of incoming stream                                                              | 56 |

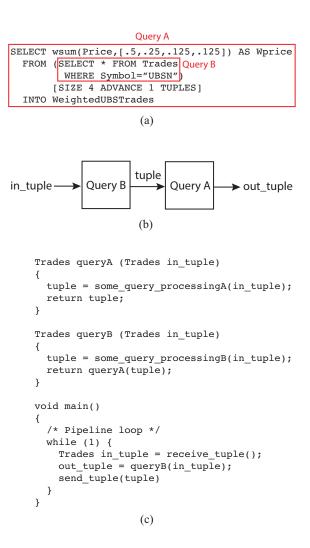

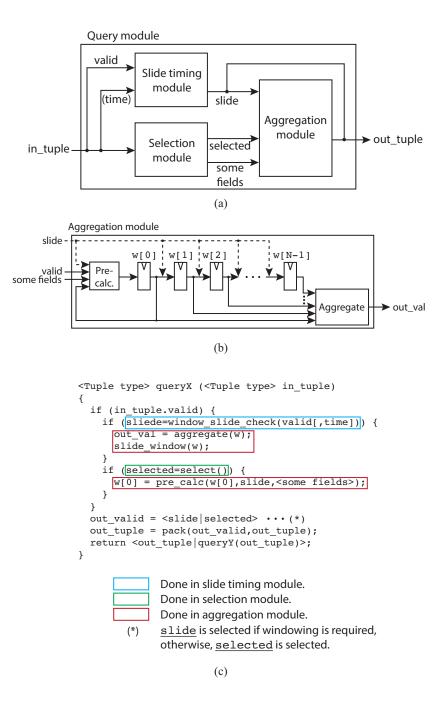

| 3.3  | C function calls for nested queries. $\ldots$                                                              | 64 |

| 3.4  | Query module architecture and its code.                                                                    | 65 |

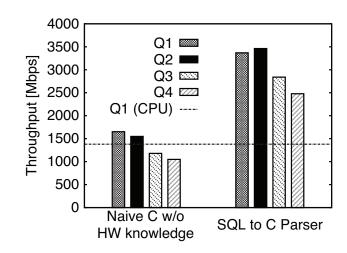

| 3.5  | Throughput comparison between naive C written without hard-                                                |    |

|      | ware development knowledge and parsed C. $\ldots$                                                          | 66 |

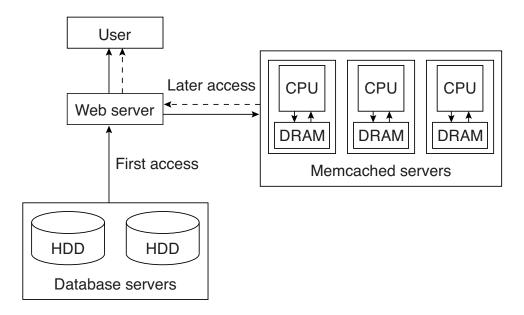

| 4.1  | The operation of memcached                                        | 73 |

|------|-------------------------------------------------------------------|----|

| 4.2  | The image of the proposed method                                  | 74 |

| 4.3  | Connection of software modules                                    | 78 |

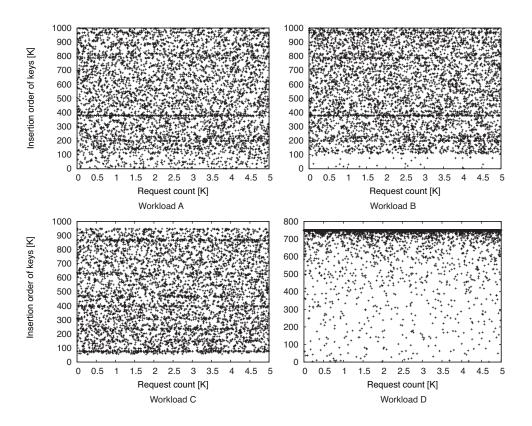

| 4.4  | Key access distribution for the first 5,000 requests. $\ldots$ .  | 79 |

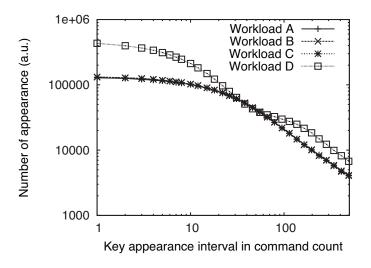

| 4.5  | Appearance interval of same keys for all workloads                | 80 |

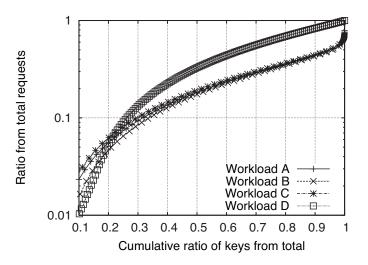

| 4.6  | Cumulative ratio of keys                                          | 81 |

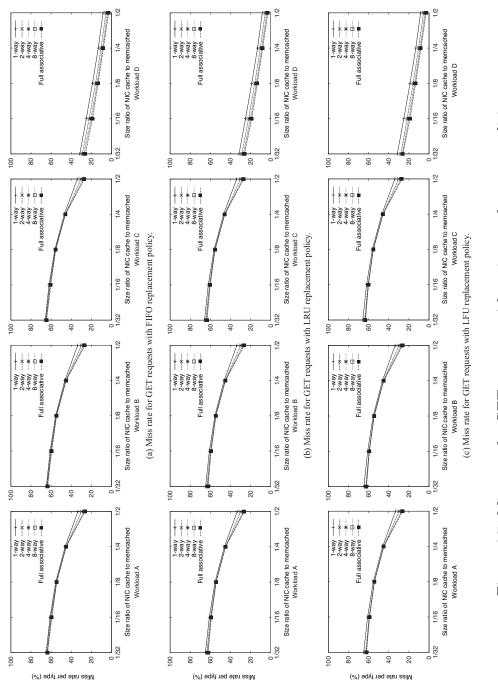

| 4.7  | Miss rate for GET requests with various replacement policies.     | 82 |

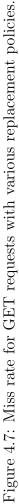

| 4.8  | Miss rates for small cache sizes for Workload A with FIFO,        |    |

|      | LRU, and LFU cache algorithms                                     | 85 |

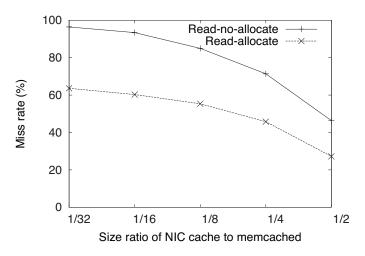

| 4.9  | Miss rates with read-allocate and read-no-allocate for Work-      |    |

|      | load C                                                            | 86 |

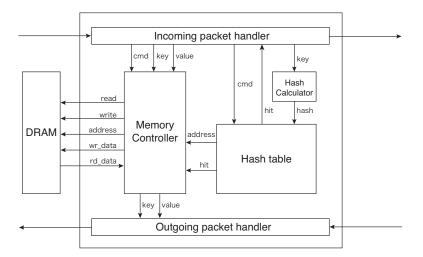

| 4.10 | NIC cache architecture                                            | 87 |

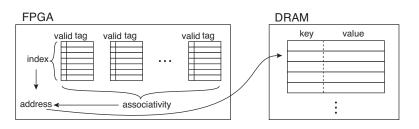

| 4.11 | Correspondence of the hash table and the value storage. $\ . \ .$ | 87 |

| 4.12 | FPGA NIC mounted on a memcached server                            | 88 |

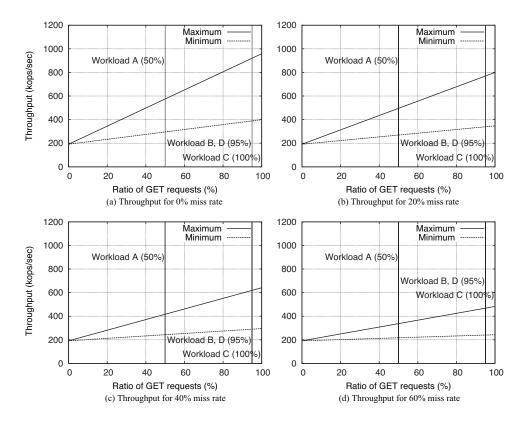

| 4.13 | Throughput of the system with various hit rates                   | 91 |

| 4.14 | Latency improvement with various associativity and cache ca-      |    |

|      | pacity                                                            | 92 |

| 4.15 | Miss rates with constant block memory size                        | 93 |

## List of Tables

| 2.1 | Performance metrics throughout the optimization process | 42 |

|-----|---------------------------------------------------------|----|

| 3.1 | Usage of input bandwidth                                | 62 |

| 4.1 | Memcached commands                                      | 73 |

| 4.2 | Description of YCSB workloads                           | 75 |

| 4.3 | Design specification of FPGA                            | 89 |

| 4.4 | Latencies of the system.                                | 89 |

| 4.5 | Throughputs of the system based on RTL simulation       | 90 |

## Chapter 1

## Introduction

## 1.1 Background

#### **1.1.1** Problems of General Purpose Processors

Since its arrival in the 1940s, the computer has always been seeking higher computation speed. This objective has been achieved through the replacement of vacuum tubes with silicon transistors, miniaturization of the silicon process, and parallelization of processors. As general-purpose processors based on von Neumann Architecture improved both from manufacturing processes and processor architecture aspects, algorithms that assume such architectures have been widely studied and improved.

After the use of computers spread widely in society, the demand for higher energy efficiency increased. Today, many people have multiple computing devices, and data centers of web service providers have tens of thousands of servers of more. Thus, reducing the power consumption or improving the energy efficiency of computers is critical for solving the ever-growing energy problem. The performance of processors has improved continuously by miniaturization of the silicon process, though Moore's law, which predicts that processor performance improvement will end in the next decade or so.

Among many solutions to this issue, using hardware dedicated for specific applications is a prospective alternative. One such hardware that is already in wide use is the Fast Fourier Transform (FFT) hardware accelerator [1]. In contrast to general-purpose processors, which have not been developed for a specific application, application-specific hardware achieves higher performance and energy efficiency in exchange for generality. However, developing application-specific hardware requires more in time and costs than developing a software application that runs on a general-purpose processor. Solving this cost issue is essential for application-specific hardware to be broadly used.

#### 1.1.2 Applications on Hardware

Dedicated hardware for a specific application achieves higher performance and energy efficiency than general-purpose processors because of the following reasons:

- Application-specific hardware gains high parallelism that is specific to the application.

- Application-specific hardware implements the instruction as hardware circuits whereas general-purpose processors fetch instructions from the memory and control the data path according to them, which leads to increased energy consumption.

However, implementing a dedicated hardware costs more than implementing software applications on a general-purpose processor in terms of time and expense for the following reasons:

- Software development and hardware development require different skills, and thus it is difficult for software engineers, who often develop the algorithm, to design hardware.

- It is necessary to extract high parallelism from the application in order to obtain high performance on dedicated hardware, and it is difficult to extract high parallelism simply by converting the software algorithm to hardware because software algorithms are intended to run on a generalpurpose processor that supposes serial processing.

- Although software can be executed immediately after writing or modifying the source code, hardware requires silicon chip manufacturing which costs millions or tens of millions of dollars.

Figure 1.1: Simplified architecture of a typical reconfigurable hardware.

Such advantages and disadvantages are significant especially for application specific integrate circuits (ASICs) and even growing as the silicon process continues to miniaturize. Recently, the increase of financial cost of manufacturing silicon chips limits the opportunities to develop application specific hardware.

#### 1.1.3 Growing Popularity of Reconfigurable Hardware

As a solution for this situation, reconfigurable hardware is attracting wide attention. Reconfigurable hardware is a hardware chip in which a hardware developer can design and modify the internal circuit after production. Generally, on a reconfigurable chip, there are logic blocks (LBs) aligned in a grid (Fig. 1.1). Each LB has a lookup table (LUT), a carry logic, and a register. A user can program the LUT in an LB so that it can have an arbitrary combinational logic. (Some reconfigurable architectures use an arithmetic logic unit (ALU) instead of LUTs.) Programming the multiplexer can configure the connections among these elements within an LB. There are wires running vertically and horizontally in the grid throughout the chip to which the LBs are connected, and the wires to be connected in the switch box can be programmed. At the intersections of the wires, there are switch boxes that can be programmed as to which vertical and horizontal wires should be connected. In addition, some memory blocks are inserted on the chip whose wire connections can be also programmed. By programming these programmable elements, an arbitrary circuit can be implemented on a reconfigurable hardware chip as long as the resource required for the application does not exceed what is available on the chip.

The circuit is usually described with Hardware Description Language (HDL) such as Verilog HDL or VHDL. The hardware description is converted to information of the LUTs, multiplexers (MUXes), and switch boxes' configuration by the tool that the reconfigurable hardware vendors provide. (This configuration file is called a bit file.) The bit file is then downloaded to the chip's configuration memory, and the chip acquires the intended behavior. Examples of reconfigurable hardware chips include field-programmable gate arrays (FPGAs) [2], programmable logic devices (PLDs) [3], coarse grained reconfigurable architecture (CGRA) [4], and a dynamically reconfigurable processor (DRP) [5], etc.

The switches that configure the on-chip interconnection and redundant wirings of reconfigurable hardware become the overhead and therefore, the performance is lower than for ASICs. This limitation made reconfigurable hardware used mainly for pre-manufacturing testing of ASICs until recently because it was difficult to implement a high performance application on reconfigurable hardware. However, as the miniaturization of the silicon process continued, reconfigurable hardware became capable of implementing sufficiently practicable circuits. Now that the cost for making ASICs has risen, there are more opportunities for reconfigurable hardware to provide a better way of accelerating an application even if the performance is lower than ASIC.

The progress of hardware development tools is another force that promotes the dedicated hardware use. (This is not only for reconfigurable hardware but also for ASICs.) Algorithms that search the hardware design space are continuously improving the performance of hardware synthesized fro HDL descriptions. Designing dedicated hardware is becoming less of an obstacle.

Figure 1.2: Replacing general purpose processors in data centers with reconfigurable hardware.

#### 1.1.4 Reconfigurable Hardware in Data Centers

Many web service providers such as Google, Amazon, Facebook, and Microsoft, run data centers that have over tens of thousands of server computers (Fig. 1.2a). Running so many computers in parallel enables the service to deal with an enormous amount of data at an enormous data rate. Moreover, the widespread use of cloud computing is moving the processes that were done in computers of individuals to data center computers and aggregating data that people and companies kept by on their own to web service providers' data centers. A natural result of this trend is that the energy consumption of data centers is becoming a growing issue. According to a report, one data center consumes as much as power as one thermal power plant can generate [6]. Companies that run data centers are eager to reduce the power consumption by improving the energy efficiency of servers and the efficiency of air conditioning of data centers.

Dedicated hardware can solve the problem that data centers are facing. As mentioned previously, dedicated hardware executes tasks faster and is more efficient than general-purpose hardware, reducing computing resources in number of processors and energy. In addition, because data centers aggregate the tasks that were scattered to individuals' and companies' computers all around the world, dedicated hardware can be more effective.

Reconfigurable hardware suits the usage in data centers for the same reasons that apply to ASICs; however, there is a specific reason that reconfigurable hardware is better than ASICs in data centers: Reconfigurable hardware can modify its functionality whenever necessary, which enables web services powered by dedicated hardware to be updated more frequently than using the more costly ASICs.

Recently, several studies have been actually trying to deploy reconfigurable hardware to data centers (Fig. 1.2b). One such work is by Microsoft Research [7]. In this work, Putnam and his group accelerated Microsoft's search engine, Bing, with FPGAs. In their system, most of the search engine is executed on general-purpose processors. However, the process called ranking, which ranks possible search results and is a costly portion of a search engine, is offloaded to FPGAs and accelerated. The experiment using 1,632 FPGA servers showed that the throughput doubled while keeping the latency the same as software. Microsoft is plans to carry out this system in production and to apply it to other applications.

A professional hardware development team that is particularly allowed to access the facilities in the data center performs this work. However, another study aims to open the reconfigurable hardware in the data center to the public. The goal is to enable end users to use FPGA resources as much as they want anytime by allocating virtual FPGA resources in the same manner as software virtual machines in Infrastructure as a Service (IaaS) [8]. This system successfully accelerated the application-level load balancer; however, further evaluation is needed. If this system is effective for various applications, it should soon become popular with many end users because the cost of the reconfigurable hardware can be shared among those who use the same hardware. Whereas every user must buy FPGA boards, costing hundreds or thousands of dollars without such a cloud system, this system will be much less expensive.

## 1.1.5 Open Issues of Reconfigurable Hardware in Data Centers

However, there are some issues that still must be solved in order to use reconfigurable hardware in data centers.

#### Hardware Development for Software Engineers

One issues is the difficulty for software engineers to develop applicationspecific hardware. Although reconfigurable hardware provides high performance and power efficiency to application developers with competitive cost, the difficulties for software developers to design dedicated hardware prevents reconfigurable hardware from being widely used by software developers (Fig. 1.2b). The reasons are as follows:

- 1. Compared to software programming languages such as C, Java and Python that are used for developing applications that run on generalpurpose processors, HDLs such as Verilog HDL and VHDL that are used for developing dedicated hardware use lower abstraction for describing the functionalities, and thus they are difficult for people to understand.

- 2. Dedicated hardware gains processing speed by parallelizing the application where general-purpose processors processes data basically serially, and various techniques are required to extract maximum parallelism without violating data dependencies.

- 3. Although general-purpose processors are based on von Neumann Architecture, dedicated hardware does not have a specific architecture, and this leads to broad design search space.

- 4. Because there are limited numbers of computing elements and memory elements on a reconfigurable hardware chip, the application developer should design the circuit so that it uses the elements in a balanced manner.

Recently, a technology called High-Level Synthesis (HLS), which synthesizes hardware circuits from codes that were written in software programming languages such as C and Java, is becoming widely used among hardware developers. Although HLS has been studied for decades, it was not until recently that they could be in practical use and become bundled to development tools provided by reconfigurable hardware vendors [9]. HLS relieved the difficulty caused by reason 1 above and reduced the time for developing hardware.

Although the remaining three difficulties have also been relieved by HLS to some extent, they still remain as challenges. Examples of possible solutions for reasons 2 and 3 are:

- to synthesize highly parallelized dedicated hardware from instruction sequence for general-purpose processors.

- Synthesize hardware from application-specific description language.

- Generate a code from software code that is easy for HLS tools to synthesize hardware.

In this study, we first clarify what is being a hurdle for software developers to develop hardware when using an HLS tool. On the basis of the perception, we propose a method based on the third method listed previously.

Reason 4 does not become an issue as long as the circuit we want to implement is small enough that it consumes only a fraction of available resources. However, when the resource usage is critical for the performance, the possible solutions include

Figure 1.3: Variations of organization of servers with reconfigurable hardware.

- offloading only the critical function to a dedicated hardware and using a general-purpose processor for everything else

- dividing the circuit into pieces and distributing them to several reconfigurable hardware chips

In this study, we assume that the circuit fits on a single chip. Although the second approach is actively studied in the community, we do not cover it in this study.

#### Architecture of Reconfigurable-hardware-powered Data Centers

Another problem of using reconfigurable hardware in data centers is that the methodology of reconfigurable hardware's usage for data centers is not established yet. Reconfigurable hardware has been used in various forms in computer systems:

- mounting a PCI Express board with reconfigurable hardware on a server with a general-purpose processor (Fig. 1.3a)

- using a reconfigurable architecture core that is integrated with a generalpurpose processor core on the same chip (Fig. 1.3b), or using such a chip mounted on a server with a general-purpose processor (Fig. 1.3c);

- using a server that has a reconfigurable hardware device and not a general-purpose processor (Fig. 1.3d).

On using reconfigurable hardware, we should be very careful to select the architecture of the system because the performance varies significantly when reconfigurable hardware is involved in the system.

Here, we will classify computer applications in two categories: real-time and non-real-time. In data centers, real-time application examples include data retrieval and stream processing, which often require low latency, and non-real-time application examples include indexing for search engines and analyzing data stored in databases that often require high throughput.

For applications that require high throughput, placement of reconfigurable hardware in the data center does not have a significant effect on the performance: what matters is whether the data source and hardware are connected with a high-bandwidth connection. Hence, an extension board with reconfigurable hardware connected to a server with a general purposeprocessor via PCI Express will fulfill the requirements as long as the bandwidth of the PCI Express is sufficient. However, for applications that require low latency, it works better if the reconfigurable hardware is placed near the network inside the server, avoiding the extra latency that occurs when placing a general-purpose processor in between the network and the reconfigurable hardware.

Figure 1.4: Two architectures of servers for reconfigurable hardware and general purpose processors.

An example of a server computer that has the network and reconfigurable hardware directly connected and a general-purpose processor is not placed in between is Maxeler Technology's MPC-X series [10]. However, this server does not have a general-purpose processor. Recently, using reconfigurable hardware and general-purpose hardware together is becoming more popular because reconfigurable hardware and general-purpose processors are good at different types of applications and the development of such a heterogeneous system is becoming easier and more efficient because of recent advances of hardware development techniques. In addition, heterogeneous systems are anticipated to be used more widely in data centers.

There are two types of architecture for using reconfigurable hardware and a general-purpose processor in combination while connecting the network directly to the reconfigurable hardware. One way is to use a server that has only reconfigurable hardware such as the aforementioned MPC-X, and connect it over a network to a regular server that has a general-purpose processor (Fig. 1.4a). The latency of networks is decreasing every year. Nevertheless, it is better not to have such latency. The other way is to place reconfigurable hardware at the network interface of the server that has a general-purpose processor (Fig. 1.4b). This architecture enables the application developers to use both the reconfigurable hardware and generalpurpose processor together with a small latency between the two devices.

Examples of works that use such architecture are research on High Frequency Trade (HFT) by NEC [11] and on Memcached by Xilinx [12]. In these systems, the FPGA at the network interface does the process that should be done at a low latency, and the general-purpose processor that is connected to the FPGA via PCI Express does the computation that uses the output of the FPGA or that the FPGA is not good at. The usage of the general-purpose processors in these works were to do only a fraction of the computation that the application requires or to do completely different computation between the FPGA and the general-purpose processor.

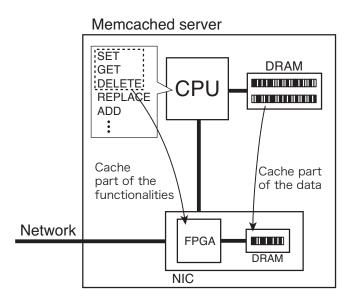

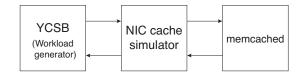

In Chapter 4, we propose a novel method of taking advantage of the architecture that places the reconfigurable hardware at the network interface of a server computer that has a general-purpose processor. In this method, the general-purpose processor and the reconfigurable hardware do basically the same computation; however, the reconfigurable hardware does only the functions that are frequently called with the frequently accessed data, and the general-purpose processor handles the rest of them. This method enables the reconfigurable hardware to process the data that comes in from the network at a low latency, and at the same time, leaves the general-purpose processor to do a variety of computations that are used less frequently. It also reduces the cost of developing the hardware system of the application because only a part of the application that is frequently used has to be implemented in hardware.

## 1.1.6 Future of Reconfigurable Hardware in Data Centers

Research continues on deploying and using reconfigurable hardware in data centers. Methods of using reconfigurable hardware over the Internet will develop approximately in three steps. First, we will use computer boards with reconfigurable hardware and a network connection. A reconfigurable hardware board that does not require mounting on a computer via PCI Express and are capable of programming from remote over the Internet will be shared among many hardware developers also software developers that are curious about developing hardware. Although some reconfigurable hardware boards are very expensive, the developer using the board is not necessarily occupying the board all the time. Thus, sharing the board will reduce its non-active period, reducing the cost for each developer. Even if reconfigurable hardware becomes available in cloud systems, this kind of form of using reconfigurable hardware will remain in the embedded system industry.

Next, reconfigurable hardware will be available for end users by allocating its resources through IaaS. This method will enable an end users to use multiple reconfigurable hardware as a computing fabric, or multiple end users to share a single reconfigurable hardware device. At this step, the developer using this method should still need the mindset and skills for developing a hardware system regardless of using RTL or HLS (Fig. 1.2b).

In the final step, the user will not notice whether the person is running a program on reconfigurable hardware or a general-purpose processor (Fig. 1.2c). This is due to the advances in hardware development technology. The compiler and the program execution environment will run the software program partially on the general-purpose processor and partially on the reconfigurable hardware while determining which is more efficient. Of course, the end user will have the option to optimize the part that is executed on reconfigurable hardware so that it will be faster and more efficient. However, as the hardware offloading technology matures, the cost of manually optimizing the hardware will come to a point that it will not compensate for the benefit of the performance improvement. This is the same situation as software compilers in that it took over the manual optimization as its compilation technique progressed.

In prospect of such future, the work we provide in this study is significant in the following perspective:

• Hardware development technology for software developers is the most important factor for introducing reconfigurable hardware to data centers. As we will go over in Chapter 2, knowing today's latest hardware development technology and analyzing the difficulties that remain will shed light as to what should happen next, which should be done regularly because the fastest and most meaningful way to advance the technology is to practice with the latest technology.

- As reconfigurable hardware goes transparent in data centers, the application running on the hardware must be written entirely in software. Extracting high performance from reconfigurable hardware with a software program is a challenging task. The work introduced in Chapter 3 achieves this goal with several kinds of reconfigurable architectures theoretically.

- When reconfigurable hardware becomes transparent in data centers, functions of applications should be executed on various computing devices such as reconfigurable hardware, general-purpose processors, and graphic processing units (GPUs), either statically or dynamically so that the application will be executed in the most efficient way. The work discussed in Chapter 4 attempts to execute a part of the application running on a general-purpose processor on a reconfigurable device.

## 1.2 Organization

In Chapter 2, we analyze the difficulties when a software developer tries to develop a dedicated hardware with an HLS tool, which is the most straight forward approach for a software developer to develop hardware. In particular, we implement an operation called *window join*, an element operator of stream processing, on DRP with *CyberWorkBench* (CWB). As a result of our stepby-step implementation, we will show what kind of knowledge a software developer would need to develop hardware.

In Chapter 3, we propose a novel method for software programmers to develop application specific hardware with reconfigurable hardware. We take StreamSQL, a description language specific to stream processing, as an example for our method and propose a parser that converts StreamSQL queries to C code intended to be synthesized to hardware configuration with an HLS tool. This method enables application developers to develop hardware by StreamSQL without having any knowledge of hardware development.

In Chapter 4, we propose a method of taking advantage of reconfigurable hardware in data centers. We accelerate a server that runs **memcached**, an in-memory key-value store, by caching its functionalities and data to its network interface card (NIC) that is equipped with an FPGA and DRAM. This method does not require any modification to the software memcached; therefore, memcached servers that are already in operation can be enhanced.

Finally, in Chapter 5, we will summarize our work and discuss what should be done in the future.

## Bibliography

- Yuehai Xu, Eitan Frachtenberg, Song Jiang, and Mike Palecezny. Very fast fourier transform algorithms hardware for implementation. *IEEE Transactions on Computers*, C-28:333–341, 1979.

- [2] R.H. Freeman. Configurable electrical circuit having configurable logic elements and configurable interconnects, September 26 1989. US Patent 4,870,302.

- [3] G. D. Electrically programmable logic circuits, June 18 1974. US Patent 3,818,452.

- [4] Reiner Hartenstein. Coarse grain reconfigurable architecture (embedded tutorial). In Proceedings of the 2001 Asia and South Pacific Design Automation Conference, pages 564–570. ACM, 2001.

- [5] Masato Motomura. A dynamically reconfigurable processor architecture. *Microprocessor Forum*, 2002.

- [6] Jonathan G Koomey. Worldwide electricity used in data centers. Environmental Research Letters, 3(3), 2008.

- [7] Andrew Putnam, Adrian M Caulfield, Eric S Chung, Derek Chiou, Kypros Constantinides, John Demme, Hadi Esmaeilzadeh, Jeremy Fowers, Gopi Prashanth Gopal, Jan Gray, et al. A reconfigurable fabric for accelerating large-scale datacenter services. In *Computer Architecture (ISCA), 2014 ACM/IEEE 41st International Symposium on*, pages 13–24. IEEE, 2014.

- [8] Stuart Byma, J Gregory Steffan, Hadi Bannazadeh, Alberto Leon Garcia, and Paul Chow. Fpgas in the cloud: Booting virtualized hardware accelerators with openstack. In *Field-Programmable Custom Computing Machines (FCCM), 2014 IEEE 22nd Annual International Symposium* on, pages 109–116. IEEE, 2014.

- [9] The open standard for parallel programming of heterogeneous systems. https://www.khronos.org/opencl/.

- [10] Maxeler: Mpc-x series. https://www.maxeler.com/products/ mpc-xseries/.

- [11] Hiroaki Inoue, Takashi Takenaka, and Masato Motomura. 20Gbps Cbased complex event processing. In Proceedings of the 2011 21st International Conference on Field Programmable Logic and Applications (FPL), 2011.

- [12] Michaela Blott, Kimon Karras, Ling Liu, Kees Vissers, Jeremia Bär, and Zsolt István. Achieving 10gbps line-rate key-value stores with fpgas. In Proceedings of the 5th USENIX Workshop on Hot Topics in Cloud Computing, pages 1–6, 2013.

## Chapter 2

## Acceleration by HLS

### 2.1 Introduction

In Chapter 1, we mentioned that it is difficult for software engineers to develop hardware. If so, what specifically is difficult? Even though HLS has made it easier for developers to design hardware with software programming languages, difficulties still remain. In this chapter, we analyze the existing difficulties through a development process of an application specific hardware with C language and an HLS tool. Furthermore, we clarify what software developers should know when they design hardware. This kind of knowledge has not been explicitly clarified because hardware developers learn it empirically. However, this knowledge should give directions to what should be improved in order to make it easier for software engineers to develop hardware.

The organization of this chapter is as follows. In Section 2.2, we explain the significance and issues in hardware stream processing. In Section 2.3, we introduce related works of developing a hardware stream processor with software. After introducing the reconfigurable hardware platform that we used in our case study in Section 2.4, we look into the details of our steps of the development and optimization of window join that we implemented on DRP with HLS tool. Then, in Section 2.6, we evaluate the performance of our window join specific hardware and clarify the viewpoints that software developer should need in order to develop a hardware system. Furthermore, we point out the effectiveness of dynamically reconfiguration feature of DRP to stream processing. Finally, we will summarize our work in Section Section 2.7.

### 2.2 Stream Processing

Stream processing [1] is attracting considerable attention as an important computation paradigm in the era of big data and cloud computing. In contrast to conventional database processing, stream processing handles numerous real-time data streams delivered through network at real-time throughput, which is conventionally realized by distributed processing on parallel servers. Although these approaches have been remarkably successful in handling the dynamic nature of incoming streams [2], there still exists increasing demand for even higher throughput. Moreover, the urgent need to reduce the ever-rising power consumption in data centers [3] indicates the limitation in relying upon such a power-hungry *scale-out* approach alone.

In view of this situation, hardware-oriented acceleration of stream processing using field-programmable gate array (FPGA) has been actively studied [4–6]. In essence, hardware customized to a given problem can achieve much higher throughput/power than a software solution that runs on generalpurpose hardware. However, such hardware solutions typically have two major drawbacks: (1) they have limited in-field flexibility and (2) software engineers find it difficult to design them. As *adaptive query* becomes an important notion in stream processing, issue (1) needs to be addressed seriously. Since stream processing requires considerable effort at the algorithm development level, owing to which this field employs mostly software engineers, issue (2) is also a fundamental problem. Actually, solving these problems on an FPGA-based framework has been an active research topic in recent years [4, 7].

The dynamically reconfigurable processor (DRP) [8] may serve as another good foundation to overcome these drawbacks from a different perspective. As will be presented in Sect. 2.4, the DRP has rich in-field flexibility and a software-friendly design environment (*i.e.*, a fairly mature C-level design tool). Since the DRP has been applied mostly in the domain of image processing applications [9] and is used by engineers with hardware knowledge, it is an interesting challenge to evaluate the performance of a DRP architecture and its design tool in solving the above-mentioned issues in stream processing.

On the basis of this observation, we carried out an experimental step-bystep implementation of adaptive stream processing on the DRP by considering *window join*, a simple but extensively studied important operation in stream processing, as a case study. Our goal in this study is to find answers to the following questions using the DRP evaluation platform:

- How and where a software source code should be modified to make it an optimized source code for hardware synthesis

- In doing so, how a software engineer should be knowledgeable and skilled in terms of hardware design

- How a state-of-the-art high-level design tool can hide hardware design details from the software programmer

- How performance varies according to different modifications

- How dynamic reconfiguration helps achieve adaptiveness of the solution

The evaluation was performed in a sequential manner, so that further insights could be obtained.

### 2.3 Related Work

Recently, several studies were conducted on hardware-accelerated stream processing. One such work uses C programming and a high-level synthesis tool [4]. This study expects the developer using this system to write simple functions e.g., arithmetic operations, aggregation, etc., and to sequence them in a regular expression. Circuits synthesized from the functions evaluate the data stream, and if the sequence of return values satisfies the given regular expression, the system asserts a signal. After its high performance being

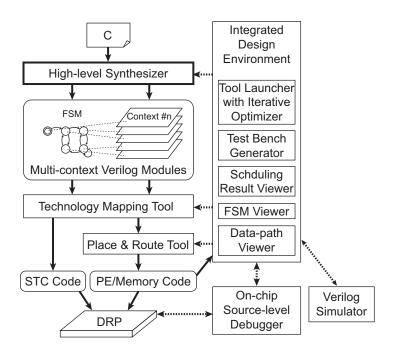

Figure 2.1: Compilation flow.

proven on an FPGA, this system has been enhanced in order to be dynamically reconfigurable, and thus queries can be modified while the system is in operation [7].

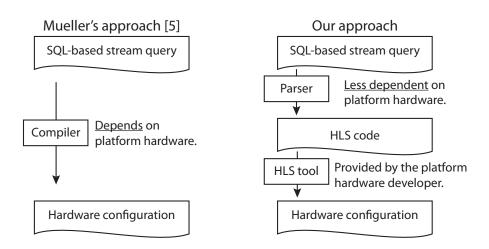

While these studies used C to describe the system discussed above, Mueller *et al.* proposed *Glacier*, a hardware synthesis system that maps SQL queries to hardware circuits [5]. The circuit consists of tiny circuit elements that correspond to stream processing operators. Mueller *et al.* demonstrated that the stream processor designed by this system and implemented on an FPGA runs faster at lower energy than a CPU. Based on this system, a dynamically reconfigurable stream processor that can switch its composition in a single clock cycle has been proposed [10].

These studies generally indicate that providing a domain-specific design framework on top of a general FPGA design platform is effective for accommodating stream processing systems in two ways: The synthesized circuits will be fast enough without requiring hardware optimizations by developers, and the system will be easier to be dynamically reconfigurable by limiting the circuits' degree of freedom. Despite lacking such a domain-specific design

Shown in architectural diagrams from Figure 6

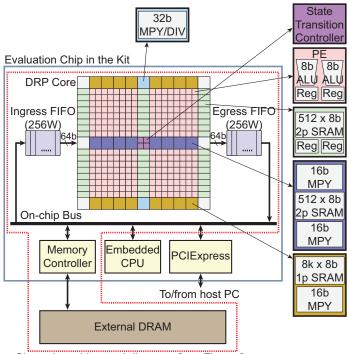

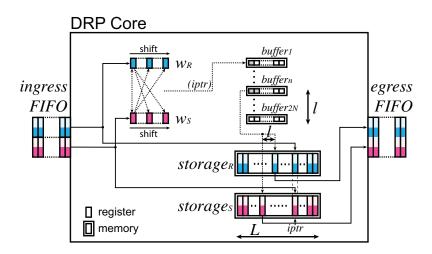

Figure 2.2: DRP hardware overview.

framework, DRP is inherently dynamically reconfigurable and has a C-based design tool, and hence it can be a platform for developing a stream processing system. To the best of our knowledge, ours is the first study to have evaluated such a system.

### 2.4 DRP: The Evaluation Platform

The dynamically reconfigurable processor (DRP) first presented in 2003 [8] features an array of small processing elements and block memories onto which user programs are compiled and mapped as hardware configurations (coarsegrained reconfigurable architecture). It features one-cycle dynamic reconfiguration; in other words, hardware configuration can switch every cycle, which is governed by a finite state machine (FSM) extracted from the user program. Essentially, reconfiguration takes place when a state transition occurs in the FSM [11].

There exists an integrated design tool for DRP based on high-level synthesis technology whose compilation flow is depicted in Fig. 2.1 [12]. It first synthesizes input source code in C into an FSM and a set of hardware con*texts*, where each context is associated with each state. FSM is compiled into state transition controller (STC, explained later) code, and the hardware contexts are mapped onto the PE/memory array. Basically, by spatially mapping each primitive operation (each data structure) onto a different PE (internal memory), inherent parallelism in given input source code is naturally extracted in the resulting customized hardware. In addition, the tool has powerful automatic optimization capabilities for enhancing the inherent parallelism, thereby shortening the critical chain of operations, and reducing the PE/memory usage, such as speculative conditional branch execution and balanced operation tree mapping. Moreover, the tool supports various programmer-controlled optimization capabilities such as *loop unrolling*, *loop* folding, and loop merging for extracting additional parallelism [11]. Overall, the tool efficiently extracts/enhances parallelism as long as data and control dependencies are maintained.

In this study, we consider a publicly available DRP evaluation kit [9]. Figure 2.2 shows the configuration of the evaluation chip used in the kit, where DRP is integrated as an on-chip IP core. The DRP core in this particular implementation has 256 PEs, 48 two-port block memories (512 B each), 16 KB one-port block memories (8 KB each), etc. (see Fig. 2.2). The DRP core is sandwiched between ingress and egress FIFOs ( $64b \times 256$  W each) that are connected to an on-chip bus (this configuration is called an STP Engine in [9].) The chip is mounted on a PCI Express card (called DRP Express) for handy evaluation using off-the-shelf PCs, on which the GUI-feature-rich tool runs.

### 2.5 Window Join on DRP

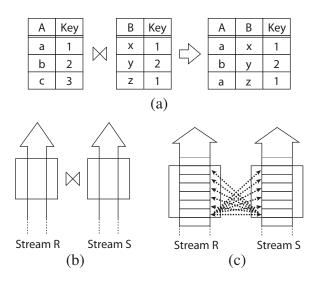

As is well known, *join* is one of the most important operators in relational data processing [1]. The basic idea of join is to combine tuples from two tables if their key fields match and create a new table (Fig. 2.3 (a)). While

Figure 2.3: Join and window join.

the number of tuples in tables is limited, that of real-time streams is infinite; therefore, an equivalent operator in stream processing introduces a *sliding window* to limit the tuples on which it joins, *i.e.*, window join (Fig. 2.3 (b)). Since streams continuously flow through the window, window join has only to compare the newly entered tuple in the R(S) stream with those in the S(R) stream's window (Fig. 2.3 (c)).

#### 2.5.1 Evaluation Strategy

Though the algorithm is simple, the window size in a realistic stream processing application tends to become very large (*e.g.*, tens of thousands), and hence, it is difficult to conduct comparisons in parallel on monolithic hardware. In view of this problem, the handshake join concept was proposed [6] and examined [13], where the window is partitioned into a series of subwindows on which window join operators are executed in parallel. In this way, a huge window join can be divided and distributed among a number of different FPGA chips. In our window join evaluation on DRP, we adopt this concept overall, and focus on designing an efficient window join operator for each sub-window. In other words, we design a system that deals with only one sub-window on DRP and we will refer to this sub-window as simply a

#### Algorithm 1 Step 1 algorithm.

```

1: loop

2:

register_R \Leftarrow ingressFIFO \Leftarrow r_t

for i \Leftarrow 0 to N - 1 do

3:

register_S \Leftarrow ingressFIFO \Leftarrow s_{t-i}

4:

if regisger_S = register_R then

5:

O \leftarrow egressFIFO \leftarrow \{register_S, register_R\}

6:

end if

7:

end for

8:

9:

(Repeat line 2 to 8 here reversing R and S, and r and s.)

t \Leftarrow t + 1

10:

11: end loop

```

"window" hereafter in this chapter.

Our window join case study begins with pure software code. Following our analysis of the inefficiency of synthesized hardware architectures, we gradually introduce optimization/modification to the source code until a fairly optimized code for hardware is arrived at. By tracing the code transitions carefully, we believe we can resolve the issues raised in Sect. 2.2.

We applied the following design parameters in the evaluation, considering the limited hardware resource on the DRP evaluation chip: (1) The size of a window (N) is set to 16 tuples and (2) each tuple in R and S streams is 32 b, with a 16 b key field and a 16 b value field. Here, key is randomly synthesized so that we can modulate the match rates. Setting of these parameters will be discussed in Sect. 2.6.

#### 2.5.2 Step 1: Pure Software Code

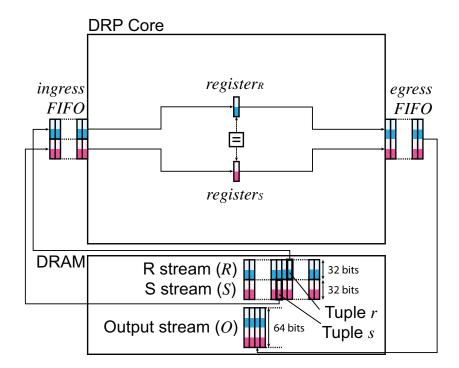

We begin with a very simple C source code appropriate for software engineers. The code substitutes tuples r(s) in streams R(S) to  $register_{R(S)}$  every time they are compared (Algorithm 1).  $Register_{R(S)}$  declared in the source code is allocated in the DRP core, which results in the hardware architecture shown in Fig. 2.4. This architecture is clearly inefficient because the same tuples are moved from an external DRAM into registers inside the DRP core

Figure 2.4: Synthesized hardware (Step 1).

repeatedly. The window join throughput (measured in terms of the incoming tuple rate) is 6.7 Mbps (Table 2.1). Table 2.1 summarizes the throughput and other performance metrics discussed further in Sect. 2.6.

#### 2.5.3 Step 2: Sliding Window Buffer

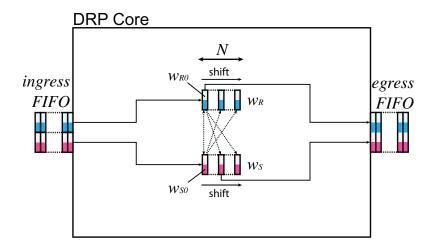

In Step 1, each tuple is read from the DRAM several times. Since external memory access has a large delay, reducing the number of accesses should improve the window join throughput. We will reduce the number of DRAM accesses by buffering the tuples that belong to the window inside the DRP. This observation makes us to declare arrays ( $w_R$  and  $w_S$ ) in the code and compare newly introduced tuples ( $w_{R0}$  and  $w_{S0}$ ) with the remaining tuples in  $w_S$  and  $w_R$  (Algorithm 2). The resultant architecture shown in Fig. 2.5 (note that the shift registers for  $w_R$  and  $w_S$  are synthesized) shows 17-fold Algorithm 2 Step 2 algorithm.

```

1: loop

for i \leftarrow N - 1 to 1 do

2:

3:

w_{Ri} \Leftarrow w_{R(i-1)}

4:

w_{Si} \Leftarrow w_{S(i-1)}

end for

5:

w_{R0,S0} \Leftarrow ingressFIFO \Leftarrow \{r_t, s_t\}

6:

for i \leftarrow 0 to N - 1 do

7:

8:

if w_{R0} = w_{Si} then

O \Leftarrow egressFIFO \Leftarrow \{w_{R0}, w_{Si}\}

9:

end if

10:

if w_{S0} = w_{Ri} then

11:

O \Leftarrow egressFIFO \Leftarrow \{w_{Ri}, w_{S0}\}

12:

end if

13:

end for

14:

t \Leftarrow t + 1

15:

16: end loop

```

throughput improvement.

#### 2.5.4 Step 3: Parallel Output Buffer

The 2N comparisons in Algorithm 2 could have been executed in parallel by allocating 2N comparators inside the DRP core since there is no data and control dependency among them. However, the synthesized hardware (Fig. 2.5) fails to exploit this parallelism. The reason is *egressFIFO*, which can take in one data item at a time, while each of the 2N comparisons may produce an output tuple.

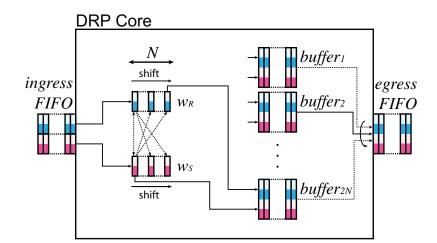

A solution to this problem is to declare 2N output buffers in the source code (Algorithm 3), so that each of the potential matches can possess a buffer to store the result. Hence, the tool can safely parallelize the 2N comparisons.  $compare_1(\cdot)$  does this 2N comparisons, concatenates the tuples whose keys matched, and returns them. One of the parallel *buffers*, on the other hand, will get the opportunity to write a tuple into *egressFIFO* ( $pop(\cdot)$ ) every main

Figure 2.5: Synthesized hardware (Step 2). Although the tuples still comes from the external DRAM, it will not be shown in this figure nor the subsequent figures in order to save space.

loop cycle (this is realized by the **for** loop that starts at line 3 and ends at line 8). Since the *buffers* are implemented as stacks, we use *push* and *pop* for accessing them. The idea is essentially to decouple parallel comparisons from serial *egressFIFO* access, which is feasible as long as the bandwidth at *egressFIFO* is lower than that at *ingressFIFO*, *i.e.*, a low match rate. The match rate issue will be discussed in Sect. 2.5.9 and 2.6.1.

We expected the tool to synthesize an architecture that achieves drastic performance improvement, as shown in Fig. 2.6. We assigned a directive (not mentioned in Algorithm 3, however, for better visibility) so that the buffers  $(buffer_{1\sim 2N})$  will be realized by registers. The throughput, however, actually reduced to 8 Mbps due to the comparisons not being done in a single cycle. This is because the parallel output buffer required more registers than what is available in a single context. When a resource shortage takes place, the synthesis tool divides the context into several contexts so that the resource usage of each context does not exceed the limit. Algorithm 3 Step 3 algorithm.

```

1: loop

2:

for i \Leftarrow 1 to 2N do

3:

for k \leftarrow N - 1 to 1 do

4:

w_{Rk} \Leftarrow w_{R(k-1)}

5:

w_{Sk} \Leftarrow w_{S(k-1)}

6:

end for

w_{R0,S0} \Leftarrow ingressFIFO \Leftarrow \{r_t, s_t\}

7:

8:

buffer_{1 \sim 2N} \Leftarrow_{push} compare_1(w_R, w_S)

O \Leftarrow egressFIFO \Leftarrow pop(buffer_i)

9:

t \Leftarrow t + 1

10:

11:

end for

12: end loop

```

#### 2.5.5 Step 4: Match Table

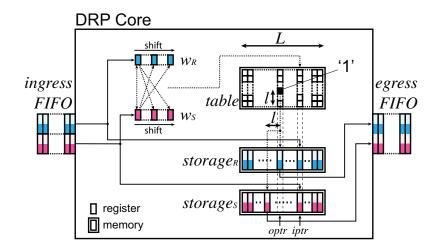

Since registers and block memories are observed to be critical resources in parallelizing an window join operation, it becomes crucial to minimize buffering requirements. Generally speaking, registers can be accessed with more parallelism, but are more expensive than block memories. Therefore, it is important to examine the usage of registers relatively more carefully. This observation leads us to re-write the code, as shown in Algorithm 4. Here,  $w_{R(S)}$  receives only the key fields, while whole tuples go to  $storage_{R(S)}$ . The function  $compare_2(\cdot)$  does the 2N comparisons between  $w_R$  and  $w_S$  and returns match results that is encoded to 32-bit-width vector. This bit vector is stored to table, which in turn points the location of matched tuples in  $storage_{R(S)}$ . The function  $output_1(\cdot)$  then returns the matched tuples to egressFIFO by acquiring appropriate tuples, which are found by decoding the bit-vector, from  $storage_{R(S)}$ . Variable l in the figure represents the difference in time between the matched tuples. It is used for encoding and decoding the location of them in the storages.

The tool synthesized the hardware architecture shown in Fig. 2.7. Note here that registers are used only for *keys* that need to be compared in parallel, and buffering requirement is reduced drastically by avoiding redundantly

Figure 2.6: Expected hardware (Step 3).

duplicating tuples to multiple output buffers (L is set to the length of *in-gressFIFO*, which is 256). The throughput recovers to 103 Mbps, since now it can conduct 2N comparisons in parallel.

The entities in the figures are realized by registers if it is depicted with single lines, and block memories if depicted with double lines. Moreover, arrays in the codes can be synthesized either by registers or block memories, and the programmer can specify which to use in the code by writing directives in the form of comments.

#### 2.5.6 Step 5: Chunk Data Prefetching

Now that the register/memory shortage is solved and comparisons can be fully parallelized, the next obvious performance bottleneck is the stream input to the DRP core. Thus far, source codes brought R and S tuples one at a time, incurring idle time in waiting for the arrival of the tuples. A solution is simply to read tuples in *chunks* so that *ingressFIFO* almost always has enough input tuples to join. This is realized by calling a DRP specific API which orders the Memory Controller to burst access the external DRAM, taking data size for its parameter. For this purpose, we set the size of each chunk to that of *ingressFIFO*. As a result, the throughput increases threefold than obtained in the previous step. Algorithm 4 Step 4 algorithm.

```

1: loop

2:

optr \Leftarrow 1

3:

for iptr \leftarrow 1 to L do

for i \leftarrow N - 1 to 1 do

4:

5:

w_{Ri} \Leftarrow w_{R(i-1)}

6:

w_{Si} \Leftarrow w_{S(i-1)}

end for

7:

w_{R0,S0}, storage_{R,S}[iptr] \leftarrow ingressFIFO \leftarrow \{r_t, s_t\}

8:

table[iptr] \Leftarrow compare_2(w_R, w_S)

9:

O \Leftarrow egressFIFO \Leftarrow output_1(table[optr], storage_{R,S})

10:

11:

if table[optr] has no positive bits then

optr \Leftarrow optr + 1

12:

end if

13:

t \Leftarrow t + 1

14:

end for

15:

16: end loop

```

#### 2.5.7 Step 6: Parallel Table Lookup

In Steps 4 and 5, there are 32 bit-slots in a single *table* entry (a bit-vector). Though the bit-vector occupies little space, decoding it is tedious for a coarsegrained architecture such as DRP. Actually, it becomes a critical path that limits the maximum operation frequency. To resolve this problem, we split the table into four 8b tables that can be handled relatively fast. This modification enables us to execute  $compare_2(\cdot)$  and  $output_1(\cdot)$  in Algorithm 4 as four parallel 8b operations that decrease the circuit delay.

In Step 5, we were treating the 32-bit column as a single variable. Therefore, the circuit became a five  $(= \log_2 32)$  stages' binary tree of OR gates that aggregates the comparison results. Each of the comparison results is shifted before being aggregated at minimum zero bits and at maximum 31 bits uniquely according to the location where the match was found. Since DRP has a 8-bit architecture, each OR gate and shifter are realized by combining four 8-bit PEs. Combining multiple PEs and realizing a PE with a larger

Figure 2.7: Synthesized hardware (Step 4).

bit width automatically is one of the HLS tool's functionalities. Overall, there was delay of six gate levels.

On the other hand, the idea of the circuit in this step is basically the same as the previous step, except that an column is treated as an 8-bit variable. Therefore, there will be one shifter and only three (=  $\log_2 8$ ) stages' binary tree of OR gates. Of course, this logic will be parallelized with four (= 32/8) identical paths, but the circuit delay will be the same. Hence there was a delay of four gate levels. Note that each gate has less delay than a gate used in Step 5, because the gate in this step does not combine multiple PEs and used as a larger gate with wider bit width.

However, since the tool divided these circuits into several contexts, the actual inter-register delay of these circuits are not so different. Instead, the number of contexts of these circuits was four in Step 5, and two in Step 6. This is the major cause of the difference between the throughput of the two architectures. As a result, the throughput improved by 83%.

#### 2.5.8 Step 7: Loop Folding (Pipelining)

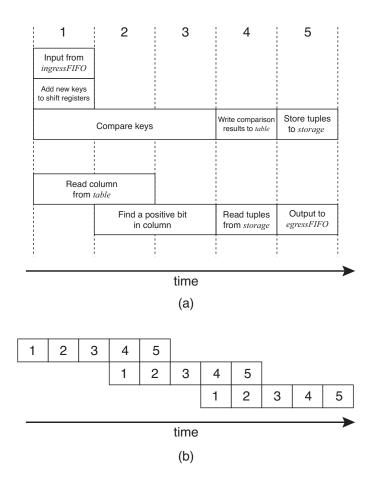

As explained in Sect. 2.4, the tool features a *loop folding* option, which essentially allows each iteration of the loop to start as early as possible, overlapping with previous iterations, as far as data/control dependencies

Figure 2.8: Timing chart of the folding.

allow. Though this is a powerful high-level synthesis feature that can extract additional parallelism, there are several conditions that should be met by the source code, *e.g.*, the code should have no inner-loops. Another tool option, *loop unrolling*, is also exploited to meet this condition here.

Figure 2.8a shows the timing of the functionalities in the main loop (each iteration takes five cycles). The tool generated a circuit that folds this loop, initiating iterations every three cycles (Fig. 2.8b). The number of cycles per main loop initiation improved to three, which was four in the previous step. The reason why the number of cycles in the main loop increased is because the tool coordinated the states by dividing them in order to maintain data dependencies. As a result, the throughput improvement at this step was

Algorithm 5 Step 8 algorithm.

1: loop 2: for  $iptr \Leftarrow 1$  to L do for  $i \leftarrow N - 1$  to 1 do 3: 4:  $w_{Ri} \Leftarrow w_{R(i-1)}$ 5: $w_{Si} \Leftarrow w_{S(i-1)}$ end for 6:  $w_{R0,S0}, storage_{R,S}[iptr] \Leftarrow ingressFIFO \Leftarrow \{r_t, s_t\}$ 7: $buf_{1\sim 2N} \Leftarrow_{push} compare_3(w_R, w_S)$ 8:  $t \Leftarrow t + 1$ 9: end for 10: for  $i \leftarrow 1$  to 2N do 11: while  $buf_i$  is not empty do 12: $O \Leftarrow egressFIFO \Leftarrow output_2(pop(buf_i), storage_{R,S})$ 13: end while 14:end for 15:16: end loop

87%.

Figure 2.9: Synthesized hardware (Step 8).

| on process.                                                         | Remarks                |                      | Pure software code | Sliding window buffer | Parallel output buffer | Match table | Chunk data prefetching | Parallel table lookup | Loop folding (pipelining) | Low match rate opt. |

|---------------------------------------------------------------------|------------------------|----------------------|--------------------|-----------------------|------------------------|-------------|------------------------|-----------------------|---------------------------|---------------------|

| imizati                                                             | Resources              | $\operatorname{Reg}$ | 88                 | 586                   | 2020                   | 235         | 326                    | 255                   | 372                       | 315                 |

| Table 2.1: Performance metrics throughout the optimization process. |                        | ALU 2pM 1pM          | 0                  | 0                     | 0                      | 0           | 0                      | 0                     | 0                         | 16                  |

|                                                                     |                        | 2 pM                 | 0                  | 0                     | 0                      | 12          | 12                     | 12                    | 16                        | 32                  |

|                                                                     |                        | ALU                  | 28                 | 119                   | 553                    | 149         | 109                    | 114                   | 215                       | 320                 |

| metric                                                              | Idle                   | [%]                  | 80.2               | 38.8                  | 3.2                    | 56.6        | 3.2                    | 5.4                   | 7.7                       | 14.7                |

| ormance                                                             | States                 | /tuple               | 98.6               | 18.8                  | 349.0                  | 14.3        | 7.4                    | 4.3                   | 3.1                       | 1.4                 |

| 2.1: Perfe                                                          | Freq                   | [MHz]                | 53                 | 55                    | 49                     | 53          | 37                     | 40                    | 56                        | 38                  |

| Table 2                                                             |                        | States               | 19                 | 105                   | 48                     | 23          | 32                     | 38                    | 32                        | 113                 |

|                                                                     | $\operatorname{Thrpt}$ | [Mbps]               | 6.8                | 113                   | 8.6                    | 103         | 311                    | 571                   | 1068                      | 1469                |

|                                                                     |                        | #                    | -                  | 2                     | က                      | 4           | Ŋ                      | 9                     | 2                         | $\infty$            |

#### 2.5.9 Step 8: Low Match Rate Optimization

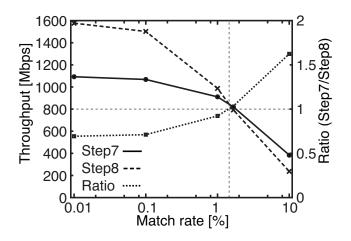

Though not explained explicitly, Steps 4 through 7 do not rely on the low match rate assumption unlike Step 3: when the match rate is high and  $storage_{R(S)}$  becomes full (iptr = L),  $output_2(\cdot)$  runs until optr reaches L and  $storage_{R(S)}$  becomes empty. However, if a low match rate is expected between the two streams, a different optimization strategy can be considered; we consider separating the  $output_2(\cdot)$ , which runs scarcely, from the main loop so that the loop can run faster.

In order to realize the architecture shown in Fig. 2.9, we rewrite the source code as in Algorithm 5. Unlike the source codes until Step 7, now it has two separate **for** loops. In addition, as a minor improvement, we replace *table* with parallel *buffers* (stacks) that hold indices of matched tuples in  $storage_{R(S)}$ . As introduced in Sect. 4.5, the variable l here represents the difference in time of matched tuples and used for encoding the location of them in the storages. The function  $compare_3(\cdot)$  does the 2N comparisons between  $w_R$  and  $w_S$  and pushes the value of *iptr* to the *buffers* which correspond to where the match was found. The function  $output_2(\cdot)$  pops one of the *buffers* and retrieves the location of matched tuples in the *storages*. In the synthesized architecture (Fig. 2.9), the first loop is successfully folded by the tool and is executed in a single cycle. The throughput is improved by 38%.

### 2.6 Discussion

#### 2.6.1 Optimization Overview

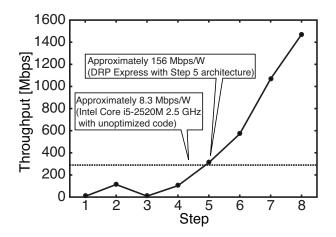

Table 2.1 summarizes the performance metrics throughout the optimization process. The reported input throughput ("Thrpt") was measured by setting the match rate to 0.1%. "States" indicates the total number of states in the synthesized FSM, while "States/Tuple" is the number of dynamic states per incoming tuple. Since the DRP can run one state per clock cycle, "Freq" (clock frequency) divided by "States/Tuple" determines the throughput if there is no "Idle" time. Here, "Idle" is due to an empty *ingressFIFO* and/or a full *egressFIFO*. Hence, code optimization is performed to improve these

three metrics.

As shown in Table 2.1, Step 1 clearly suffers from excessive "idle" cycles. This is because a certain number of idle cycles occurs each time the DRP Core accesses the DRAM, and the system brings the same tuples several times. As we explained in Sect. 2.5.3, we reduced the numbers of DRAM access in Step 2. You can see the percentage of idle cycles reduced just by reducing the number of DRAM accesses. However, not being able to compare the keys in the shift registers in parallel, Step 2 still takes about 19 states on average per tuple.