## 博士論文

Neuromorphic systems performing early-sensory and cognitive processing with CMOS devices

生体の初期感覚および知覚情報処理を模擬する CMOS 集積回路に関する研究

Graduate School of Information Science and Technology Hokkaido University

北海道大学 大学院情報科学研究科

GESSYCA MARIA TOVAR NUNEZ ジェシカ マリア トヴァー ヌニエス

Feb. 2011

### Acknowledgments

First, I would like to thank my supervisor Prof. Tetsuya Asai. I could not have imagined having better advisor, he is an excellent teacher, providing me encouragement, and giving me good advice, and good ideas.

My appreciation also goes to Prof. Yoshihito Amemiya for his support, help and understanding throughout my studies. My sincere thanks are due to Prof. Kanji Yoh and Prof. Yasuo Takahashi, the official referees of this thesis.

I would also like to thank my colleagues. I'm especially grateful to Akira Utagawa for assisting me in many different ways through all the graduate studies.

During my graduate studies, I worked with many students and former faculty staff. My thanks to Andrew Kilinga Kikombo and Ken-ichi Ueno, for fruitful discussion and constructive advices through my studies. My thanks also go to Dr. Hirose and Dr. Oya for their motivation.

Finally but definitely not the least, I wish to thank my parents Gessy Nuñez de Tovar and Jesus Tovar. They raised me, taught me, supported me and love me. Without them I would not be the person I am today. The same goes to the rest of my family. I would like to extend my sincere thanks to Fumi Kobayashi for her extended support through my graduate studies.

To them I want to dedicate this thesis.

### Neuromorphic systems performing early sensory and cognitive processing with CMOS devices

### Abstract

This research aims at implementing "Neuromorphic Systems", i.e., circuits inspired by the organizing principles of animal neural systems, implemented using standard Complementary Metal-Oxide Silicon (CMOS) LSI technology. These kinds of circuits are usually parallel, and they respond in real time. They operate mainly in the sub-threshold region, where the transistors have physical properties that are useful for emulating neurons and neural systems, such as thresholding and exponentiation. Based on current knowledge of biological systems, this work aims at developing neural circuits and systems that emulate basic functions of the sensory system. The sensory system is the part of the nervous system responsible for processing sensory information, it consists of sensory receptors, neural pathways, and other parts of the brain involved in sensory perception. Sense perception depends on sensory receptors that respond to various stimuli. When a stimulus triggers an impulse in a receptor, the stimulus is transformed into pulses or action potentials. The action potential travels through a pathway to the cerebral cortex, where they are processed and interpreted. To this end, this research starts with the implementation of some functions of the early-sensory processing like, detection and transformation of input stimuli, role synaptic connections in sensory information processing. This is done by implementing a number of models such as, a) a temperature sensor, (somatosensory system), inspired by the operation of neurons in sea slugs and snails, in order to mimic sensory receptors whose function is to transform physical stimuli into a train of nerve impulses, b) this neuron model was extended for implementing a network for weak signal detection that exhibit tolerance to noises, to explore the ability of sensory systems to exploit noises inherit in their own elements (neurons) as well as noises from the environment (i.e. the input

stimuli), and c) the circuit implementation of a depressing synapse model, whose dynamic effects possibly have a functional role in encoding information brought by sensory stimuli. In auditory pathway, depressing synapses may provide an effective way of detecting emergent synchrony in afferent activities. Then, the attention is shifted to the cognitive processing area with the introduction of two models. a) a neural network for sensory segmentation. To analyze and understand natural scenes, i.e., images, sounds, etc. it is necessary to decompose the scene into coherent "segments", where each segment corresponds to a different component of the scene. This ability is known as sensory segmentation. The model consists of mutually coupled neural oscillators that exhibit synchronous (or asynchronous) activity. The basic idea is to strengthen (or weaken) the synaptic weights between synchronous (or asynchronous) neurons, which may result in phase-domain segmentation. Finally, this work concludes with b) the implementation of a neural model for the storage of temporal sequences. In order to study the brain ability to learn and recall information as the environment changes over time (i.e. information we perceive is time varying) which is of fundamental importance in various sensory functions. The model consists of neural oscillators coupled to a common output cell. The basic idea is to learn input sequences, by superposition of rectangular periodic activity (oscillators) with different frequencies. To mimic the operation of these neurons and networks of neurons, we employed biological nonlinear oscillators. The mathematical model of these oscillators consist of two nonlinear differential equations whose main term is a sigmoid function. The stability of the model depends on the magnitude of its variables. In other words, the model can be excitatory or oscillatory depending on the value of its variables. The models were implemented with basic circuits such as differential pairs (which emulate a sigmoid-like operation) and current mirrors. The operations of the systems were investigated through theoretical analysis, numerical simulations and circuit simulations. The implication of device fabrication mismatches and environmental noise were also studied.

## Contents

| 1        | Intr          | oduction                                                                           | 12        |

|----------|---------------|------------------------------------------------------------------------------------|-----------|

|          | 1.1           | Background                                                                         | 12        |

|          | 1.2           | Objective                                                                          | 13        |

| <b>2</b> | Ba            | sic concepts                                                                       |           |

|          | $\mathbf{CM}$ | OS circuits and neural networks                                                    | <b>20</b> |

|          | 2.1           | CMOS circuits                                                                      | 20        |

|          |               | 2.1.1 The MOSFET                                                                   | 21        |

|          |               | 2.1.2 Sub-threshold current                                                        | 25        |

|          |               | 2.1.3 Sub-threshold analog circuits                                                | 26        |

|          | 2.2           | Introduction to neural networks                                                    | 31        |

|          |               | 2.2.1 Neurons                                                                      | 31        |

|          |               | 2.2.2 Artificial neural networks                                                   | 32        |

|          |               | 2.2.3 Processing elements transfer function                                        | 34        |

|          |               | 2.2.4 Learning                                                                     | 37        |

|          | 2.3           | Summary                                                                            | 39        |

| 3        | Ten           | aperature receptor circuit                                                         | 40        |

|          | 3.1           | The model                                                                          | 42        |

|          |               | 3.1.1 Stability of the Wilson-Cowan system                                         | 48        |

|          | 3.2           | Circuit implementation                                                             | 49        |

|          | 3.3           | Simulations and experimental results                                               | 51        |

|          | 3.4           | nMOS transistor with temperature dependence                                        | 58        |

|          | 3.5           | Differential pair with temperature dependence                                      | 60        |

|          | 3.6           | Summary                                                                            | 62        |

| 4        | Noi           | se in neural network                                                               | 64        |

|          | 4.1           | Model and numerical simulations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 65        |

|          | 4.2           | Circuit implementation                                                             | 69        |

|          | 4.3           | Simulations results                                                                | 71        |

|          | 4.4           | Summary                                                                            | 75        |

### CONTENTS

| <b>5</b> | Dep  | ressing synapses and synchronization                          | <b>76</b> |

|----------|------|---------------------------------------------------------------|-----------|

|          | 5.1  | Network model                                                 | 77        |

|          | 5.2  | Circuit implementation                                        | 78        |

|          | 5.3  | Simulation results                                            | 82        |

|          | 5.4  | STDP learning circuit                                         | 85        |

|          | 5.5  | Summary                                                       | 89        |

| 6        | Sens | sory segmentation                                             | 90        |

|          | 6.1  | Model and basic operation                                     | 91        |

|          | 6.2  | $Circuit\ implementation\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$ | 96        |

|          | 6.3  | Summary                                                       | 103       |

| 7        | Stor | age of temporal sequences                                     | 104       |

|          | 7.1  | Model                                                         | 105       |

|          | 7.2  | $Circuit\ implementation\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$    | 111       |

|          | 7.3  | Simulation results                                            | 117       |

|          | 7.4  | Summary                                                       | 122       |

| 8        | Con  | clusion                                                       | 124       |

5

# List of Figures

| 1.1  | Route followed by the different inputs of the sensory system           | 15 |

|------|------------------------------------------------------------------------|----|

| 1.2  | General outline of the ascending pathway                               | 15 |

|      |                                                                        |    |

| 2.1  | Symbols used to denote the MOSFET devices                              | 21 |

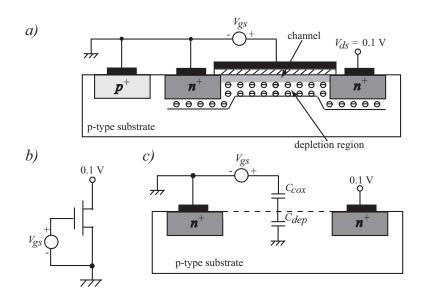

| 2.2  | Simplified structure of an n-channel MOSFET                            | 21 |

| 2.3  | a) Structure of an nMOS transistor with gate voltage $V_{gs}$ , b)     |    |

|      | corresponding symbology, and c) nMOS showing the depletion             |    |

|      | capacitance                                                            | 22 |

| 2.4  | $I_d$ - $V_{ds}$ characteristic of an nMOS. ( $V_{ds}$ is small)       | 23 |

| 2.5  | nMOS transistor channel after applying $V_{ds}$                        | 23 |

| 2.6  | $I_d$ - $V_{ds}$ characteristic of an nMOS transistor                  | 24 |

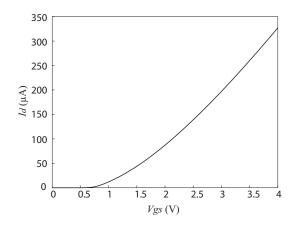

| 2.7  | $I_d$ - $V_{gs}$ characteristic of an nMOS transistor                  | 25 |

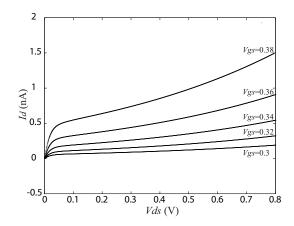

| 2.8  | $I_d$ - $V_{ds}$ characteristic of an nMOS transistor operating in the |    |

|      | sub-threshold region.                                                  | 25 |

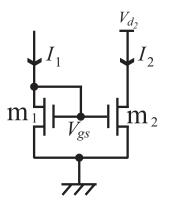

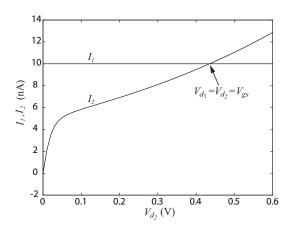

| 2.9  | Current mirror circuit.                                                | 27 |

| 2.10 | Current mirror simulation results.                                     | 27 |

| 2.11 | Schematic of the differential pair.                                    | 28 |

| 2.12 | Differential pair output currents as function of $V_1 - V_2$           | 29 |

| 2.13 | Transconductance amplifier, a)schematic, b) symbol                     | 30 |

| 2.14 | Transconductance amplifier output current                              | 30 |

| 2.15 | Typical neuron.                                                        | 32 |

| 2.16 | Basic artificial neuron.                                               | 33 |

| 2.17 | Processing elements (PE) transfer functions                            | 35 |

|      |                                                                        |    |

| 3.1  | Temperature Receptor operation model                                   | 41 |

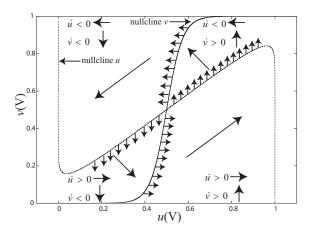

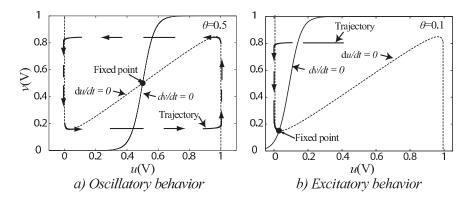

| 3.2  | u and $v$ nullclines with vector field direction.<br>                  | 42 |

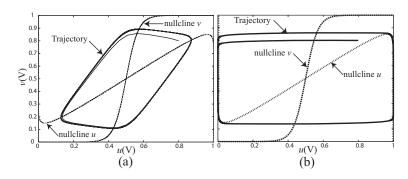

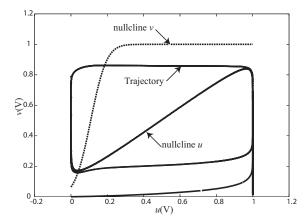

| 3.3  | Trajectory when a) $\tau = 1$ and b) $\tau << 1. \dots \dots \dots$    | 42 |

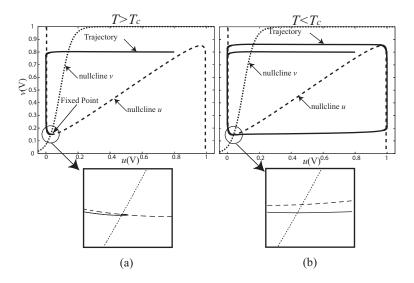

| 3.4  | Nullclines showing the fixed point and the trajectory when a)          |    |

|      | system is stable b) system is oscillatory                              | 43 |

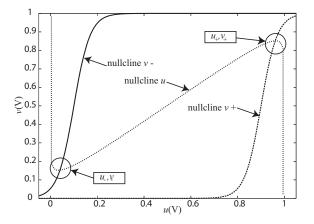

| 3.5  | u and $v$ local maximum and local minimum                              | 44 |

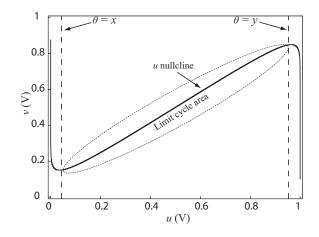

| 3.6  | Threshold values $x$ and $y$ showing the area where the system is                                           |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | oscillatory                                                                                                 | 45 |

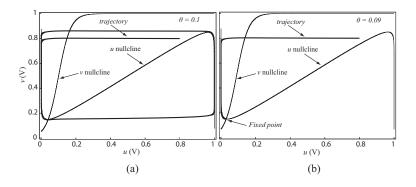

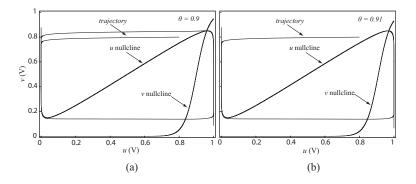

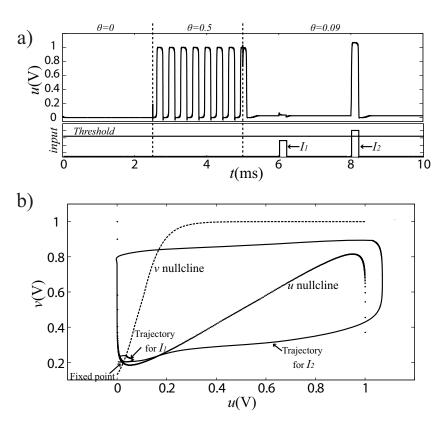

| 3.7  | Nulclines and trajectories when a) $\theta=0.1$ and b) $\theta=0.09.~$                                      | 45 |

| 3.8  | $v$ nullcline when $\theta = 0.1$ and $\theta = 0.09$                                                       | 46 |

| 3.9  | Nulclines and trajectories when a) $\theta=0.9$ and b) $\theta=0.91.$                                       | 46 |

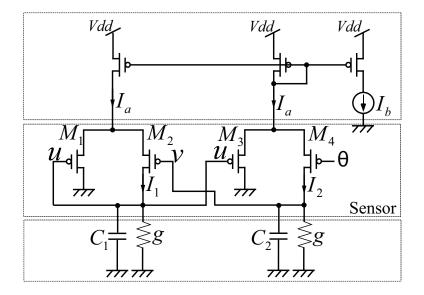

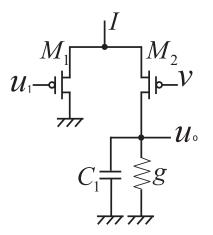

| 3.10 | Temperature receptor circuit.                                                                               | 47 |

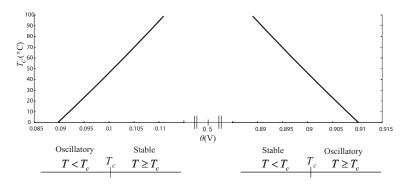

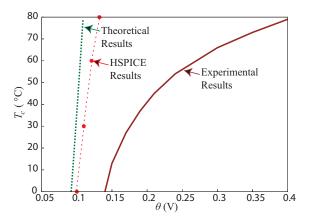

| 3.11 | Relation between $\theta_{\pm}$ and $T_c$ .                                                                 | 47 |

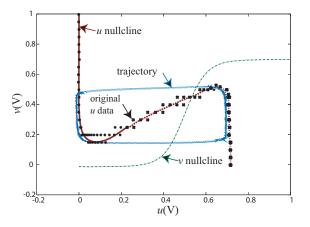

| 3.12 | Trajectory and nullclines obtained through simulation results when                                          |    |

|      | the system is oscillatory                                                                                   | 47 |

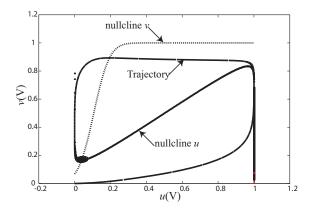

| 3.13 | Simulation results when the system is stationary                                                            | 49 |

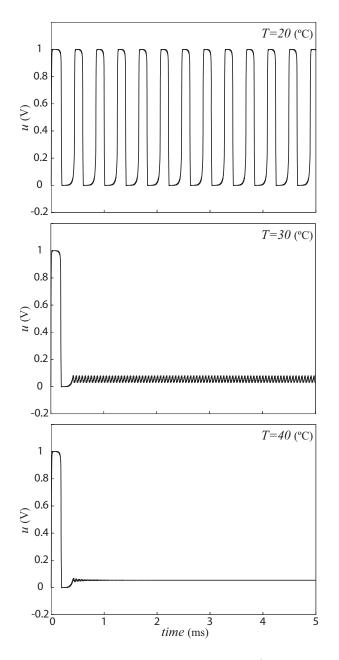

| 3.14 | Waveform of $u$ at different temperatures (from $T = 20^{\circ}$ C to $T =$                                 |    |

|      | $40^{\circ}$ C)                                                                                             | 54 |

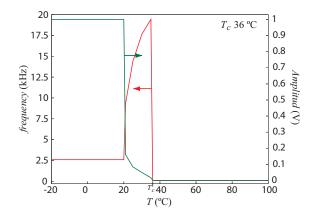

| 3.15 | Oscillation frequencies of the circuit. $(T_c = 36^{\circ}C)$                                               | 55 |

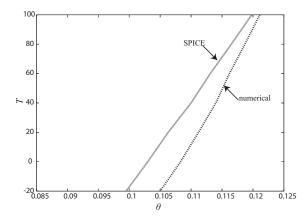

| 3.16 | Relation between $\theta_{\pm}$ and $T_c$ obtained through numerical and cir-                               |    |

|      | cuit simulations. $\ldots$ | 55 |

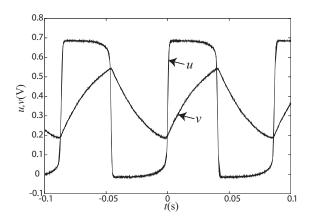

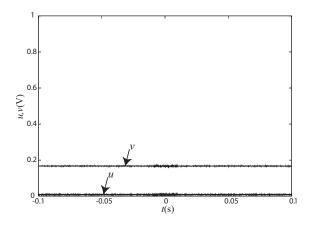

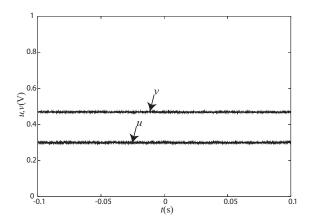

| 3.17 | Experimental results: $\theta = 170 \text{ mV}$ at $T = 23^{\circ}\text{C}$ (oscillatory state).            | 55 |

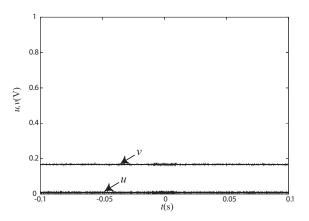

| 3.18 | Experimental results: $\theta = 150 \text{ mV}$ at $T = 23^{\circ}\text{C}$ (stationary state).             | 56 |

| 3.19 | Circuit used for calculation of the $u$ nullcline                                                           | 56 |

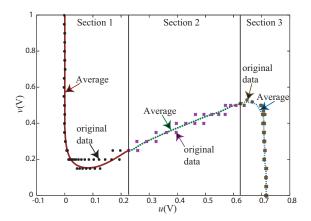

| 3.20 | Sections used for the calculation of the $u$ nullcline                                                      | 56 |

| 3.21 | Experimental nullclines and trajectory                                                                      | 57 |

| 3.22 | Bias voltage vs temperature, experimental results                                                           | 57 |

| 3.23 | Stationary state with $\theta = 140 \text{ mV}$ and $T = 23^{\circ}\text{C}$                                | 57 |

| 3.24 | Stationary state with $\theta = 140 \text{ mV}$ and $T = 75^{\circ}\text{C}$                                | 58 |

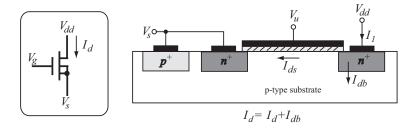

| 3.25 | nMOS transistor structure showing leak current                                                              | 58 |

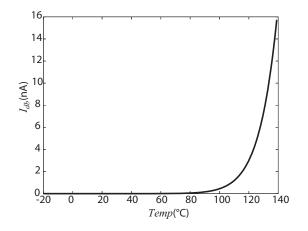

| 3.26 | Drain-bulk current $I_{db}$ vs <i>Temperature</i>                                                           | 59 |

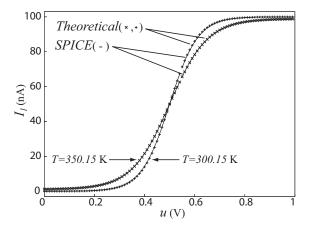

| 3.27 | Differential pair.                                                                                          | 59 |

| 3.28 | Theoretical and SPICE results of differential pair's current $I_1$                                          |    |

|      | when temperature is 300.15 K and 400.15 K. $\ldots$                                                         | 60 |

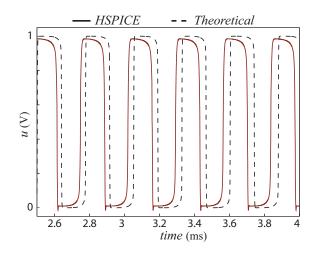

| 3.29 | $\label{eq:comparison} \mbox{Comparison of temperature receptor oscillations, between HSPICE}$              |    |

|      | results and theoretical results without leak currents. $T=127\ ^\circ C$                                    | 61 |

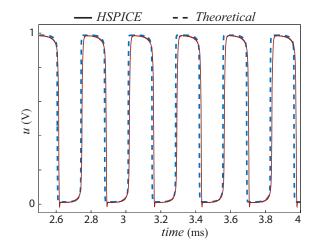

| 3.30 | $\label{eq:comparison} \mbox{Comparison of temperature receptor oscillations, between HSPICE}$              |    |

|      | results and theoretical results including leak currents. $\hdots$                                           | 62 |

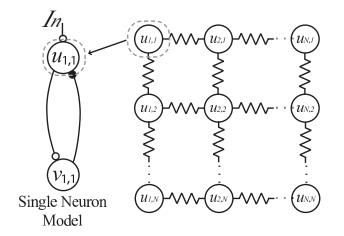

| 4.1  | Network model                                                                                               | 66 |

| 4.2  | Nullclines of a single oscillator for different $\theta$ s                                                  | 66 |

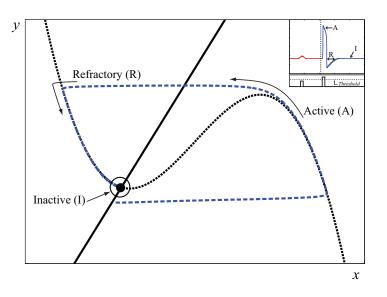

| 4.3  | Nullclines and activity of a typical excitable system (Fitz-Hugh                                            |    |

|      | Nagumo) showing the different operation states. $\hdots$                                                    | 68 |

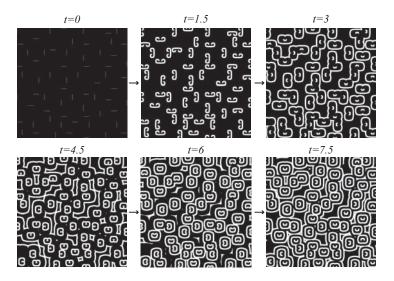

| 4.4  | Numerical results of $1000 \times 1000$ network with $\theta = 0.1$ (excitatory                             |    |

|      | behavior)                                                                                                   | 69 |

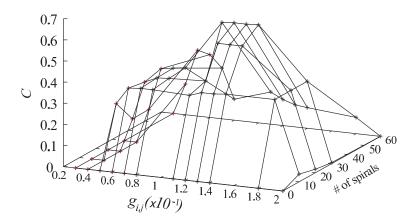

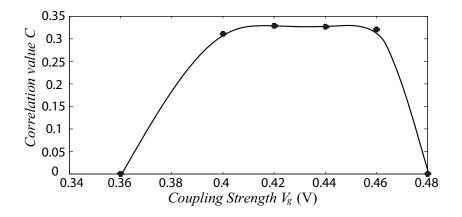

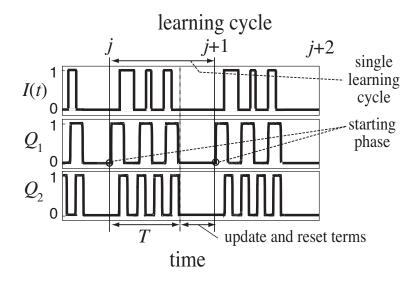

| 4.5        | Numerical results showing the Correlation value vs coupling strength        |    |

|------------|-----------------------------------------------------------------------------|----|

|            | and noise levels                                                            | 70 |

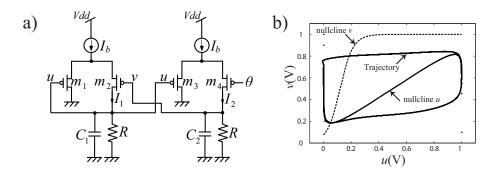

| 4.6        | Single neural oscillator circuit and circuit's nullclines                   | 71 |

| 4.7        | Simulation results of the neural oscillator circuit.                        | 72 |

| 4.8        | Circuit simulations results showing the wave propagation of the             |    |

|            | circuit with $10 \times 10$ neurons                                         | 73 |

| 4.9        | Circuit simulations results showing the correlation vs the coupling         |    |

|            | strength with $100 \times 100$ neurons                                      | 73 |

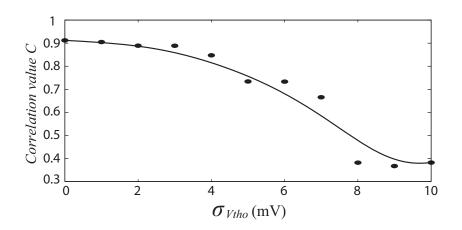

| 4.10       | Numerical simulations of the circuit dynamic showing the corre-             |    |

|            | lation vs the threshold variation of bias current transistor in a           |    |

|            | network of $1000 \times 1000$ neurons                                       | 74 |

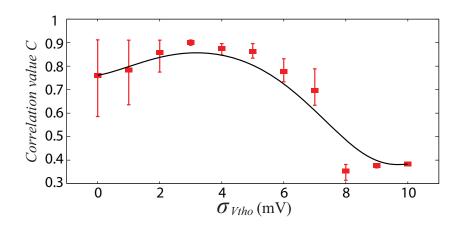

| 4.11       | Numerical simulations of the circuit dynamic showing the cor-               |    |

|            | relation C vs the threshold variation $\sigma_{Vtho}$ for different initial |    |

|            | conditions in a network of $1000 \times 1000$ neurons                       | 75 |

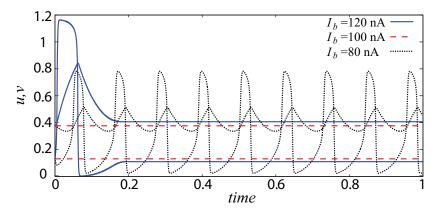

| 4.12       | Neuron behavior for different values of bias current $I_b$                  | 75 |

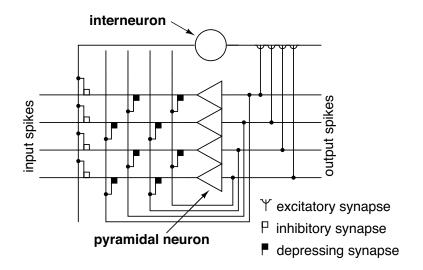

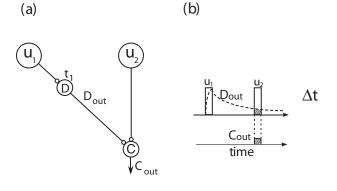

| 5.1        | Neural network model for precisely-timed pulse synchronization .            | 78 |

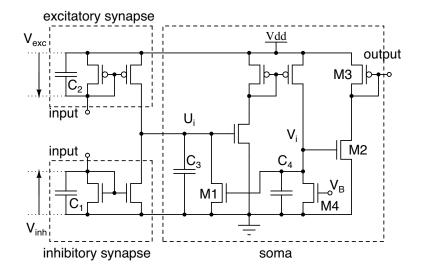

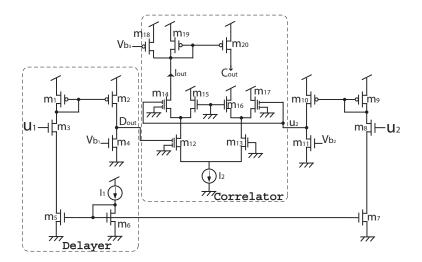

| 5.1<br>5.2 | Neuron circuit with conventional excitatory and inhibitory synapses         | 80 |

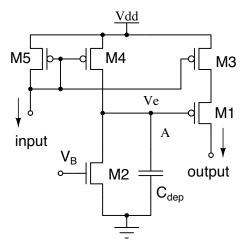

|            | Depressing synapse circuit                                                  |    |

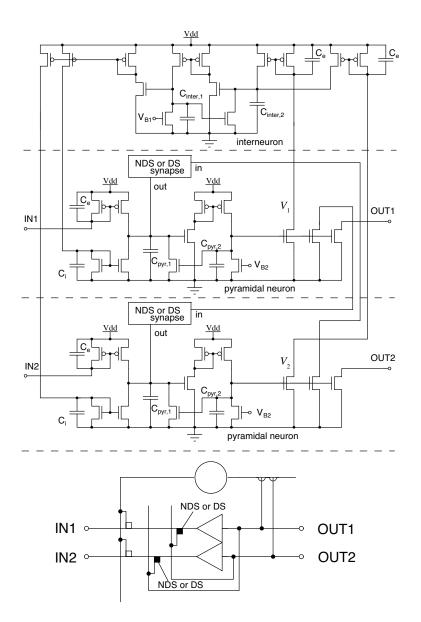

| 5.3<br>E 4 | Circuit diagram of network model with two pyramidal neurons                 | 80 |

| 5.4        | and one interneuron: Each pyramidal neuron circuit has positive             |    |

|            | feedback connection through nondepressing (NDS) or depressing               |    |

|            | synapses (DS).                                                              | 81 |

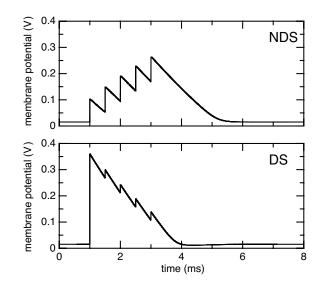

| 5.5        | Membrane potentials of pyramidal neuron circuits for short time             | 01 |

| 0.0        | input spike trains through nondepressing (NDS) or depressing                |    |

|            | synapses (DS)                                                               | 82 |

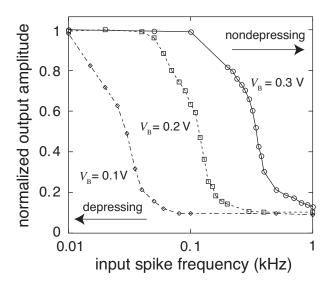

| 5.6        | Changes in amplitude of output of depressing synapse circuit                | 02 |

| 5.0        | against firing rate of presynaptic neuron                                   | 83 |

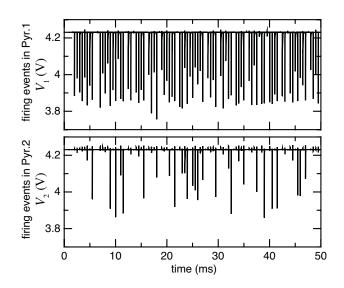

| 5.7        | Output pulses train of pyramidal neuron circuits with nonde-                | 00 |

| 0.1        | pressing synapses                                                           | 84 |

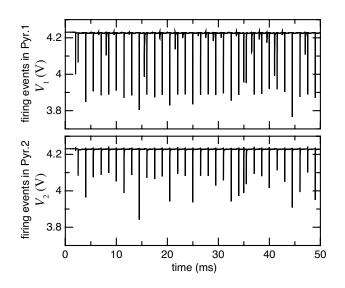

| 5.8        | Output pulses train of pyramidal neuron circuits with depressing            | 04 |

| 0.0        | synapses                                                                    | 85 |

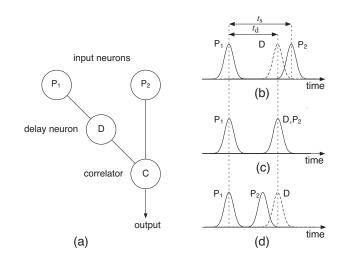

| 5.9        | (Primitive correlation neural network consisting of two input neu-          | 00 |

| 0.9        | rons ( $P_1$ and $P_2$ ), delay neuron (D), and correlator (C)              | 86 |

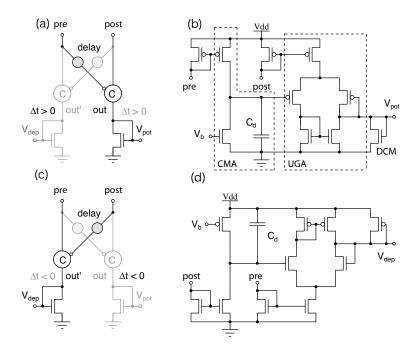

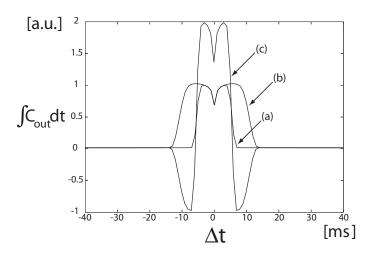

| 5 10       | Spike-timing detectors                                                      | 87 |

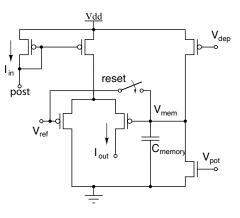

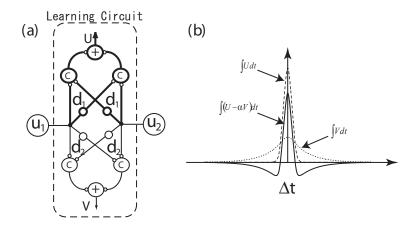

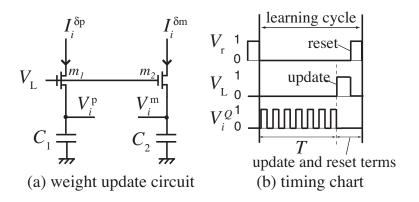

|            | Analog memory circuit for weight storage                                    | 88 |

|            |                                                                             |    |

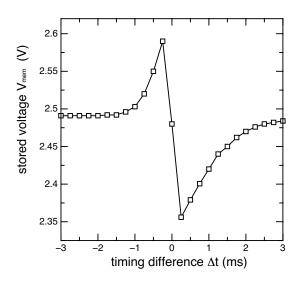

| 0.12       | Simulation results of spike-timing dependent plasticity circuit             | 88 |

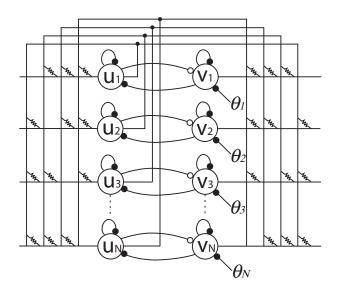

| 6.1        | Network construction of segmentation model                                  | 91 |

| 6.2        | Reichardt's correlation network                                             | 92 |

8

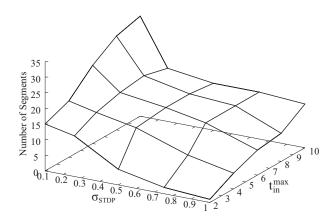

| 6.3                                                                                                                                                          | Learning characteristic: Reichardt's correlation                                     | 92                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 6.4                                                                                                                                                          | spike-timing dependent plasticity (STDP) learning Model                              | 94                                                                      |

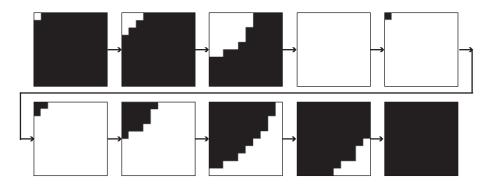

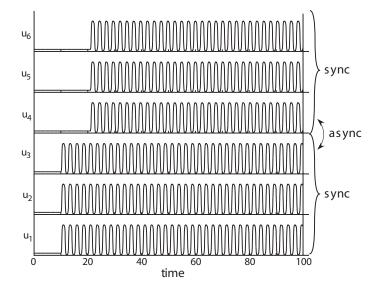

| 6.5                                                                                                                                                          | Numerical simulation results                                                         | 95                                                                      |

| 6.6                                                                                                                                                          | simulation results showing segmentation ability of the network .                     | 96                                                                      |

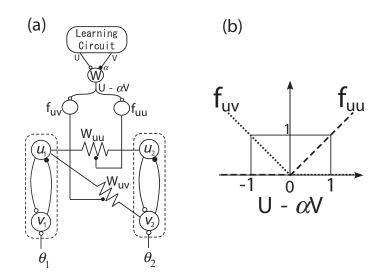

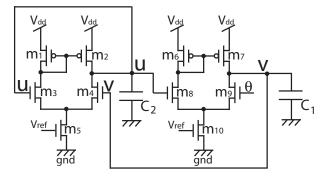

| 6.7                                                                                                                                                          | Unit circuits for neural segmentation                                                | 96                                                                      |

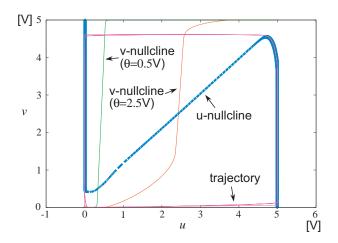

| 6.8                                                                                                                                                          | Nullclines and trajectory for $\theta = 2.5$ V obtained from circuit                 |                                                                         |

|                                                                                                                                                              | simulations.                                                                         | 97                                                                      |

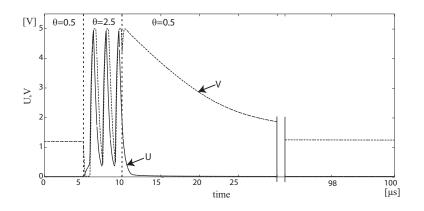

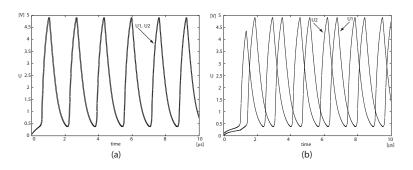

| 6.9                                                                                                                                                          | Simulation results of neural oscillator.                                             | 97                                                                      |

| 6.10                                                                                                                                                         | spike-timing dependent plasticity circuit                                            | 99                                                                      |

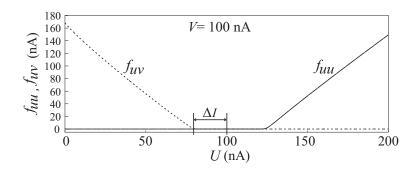

| 6.11                                                                                                                                                         | spike-timing dependent plasticity characteristics                                    | 100                                                                     |

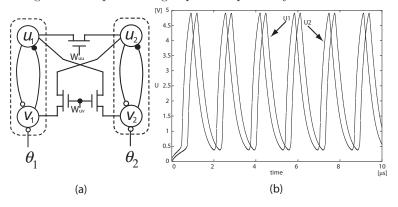

| 6.12                                                                                                                                                         | (a) Coupled neural oscillators (b) $u_1$ and $u_2$ oscillations                      | 100                                                                     |

| 6.13                                                                                                                                                         | oscillation of neurons $u_1$ and $u_2$ when (a) excitation is applied and            |                                                                         |

|                                                                                                                                                              | (b) inhibition is applied.                                                           | 101                                                                     |

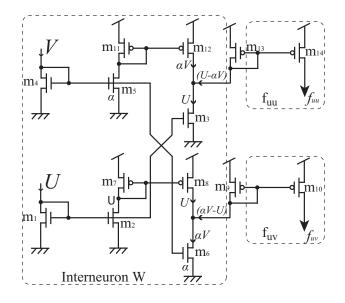

| 6.14                                                                                                                                                         | interneuron circuit                                                                  | 101                                                                     |

| 6.15                                                                                                                                                         | circuit simulation results of interneuron circuit                                    | 102                                                                     |

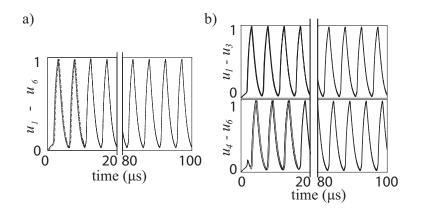

| 6.16                                                                                                                                                         | circuit simulation results for a) inter-spike interval $\Delta t = 0$ , and          |                                                                         |

|                                                                                                                                                              | b) $\Delta t = 3 \ \mu s.$                                                           | 102                                                                     |

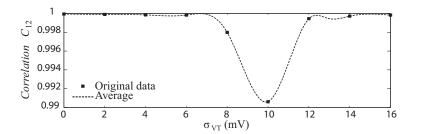

| 6.17                                                                                                                                                         | correlation values between neurons $u_1$ and $u_2$ for different $\sigma_{\rm VT}$ . | 103                                                                     |

| 6.18                                                                                                                                                         | correlation values between neurons $u_1$ and $u_3$ for different $\sigma_{\rm VT}$ . | 103                                                                     |

|                                                                                                                                                              |                                                                                      |                                                                         |

| <b>F</b> 1                                                                                                                                                   |                                                                                      | 100                                                                     |

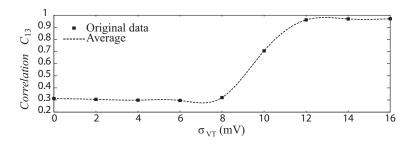

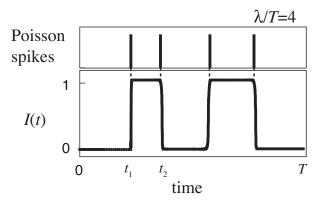

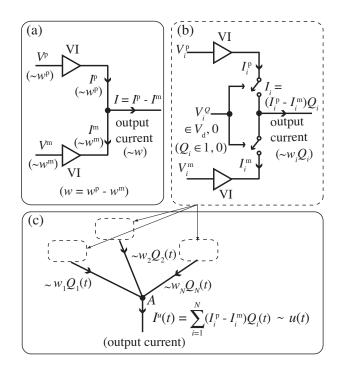

| 7.1                                                                                                                                                          | Proposed temporal coding model.                                                      |                                                                         |

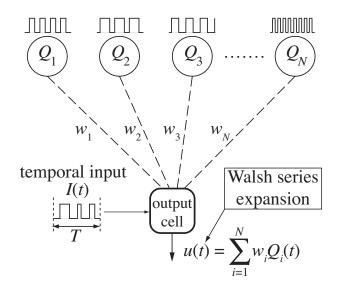

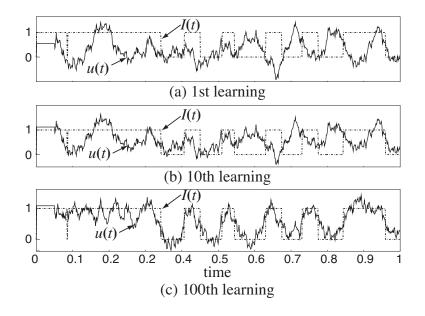

| 7.2                                                                                                                                                          | Definition of single learning cycle                                                  |                                                                         |

|                                                                                                                                                              | Definition of single learning cycle                                                  |                                                                         |

| 7.2                                                                                                                                                          | Definition of single learning cycle                                                  | 107                                                                     |

| 7.2<br>7.3                                                                                                                                                   | Definition of single learning cycle                                                  | 107<br>108                                                              |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li></ul>                                                                                                                | Definition of single learning cycle                                                  | 107<br>108<br>109                                                       |

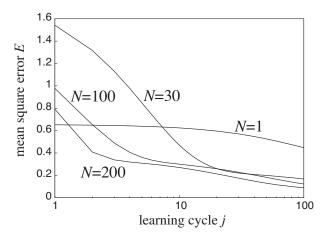

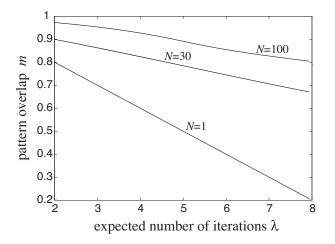

| <ul><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                                                                                    | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109                                                |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul>                                                                                  | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109<br>110                                         |

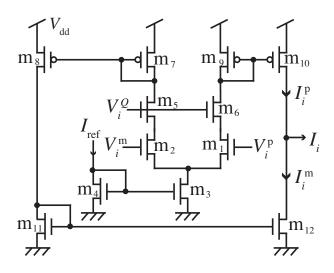

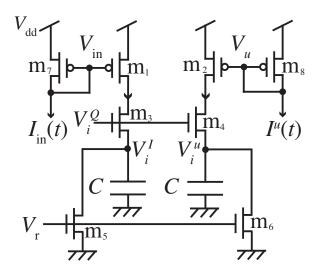

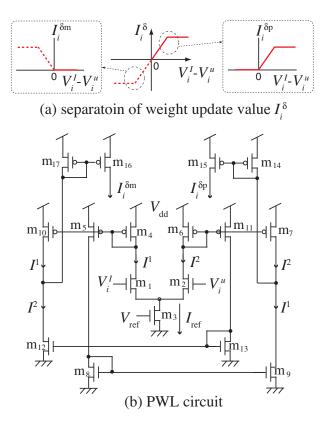

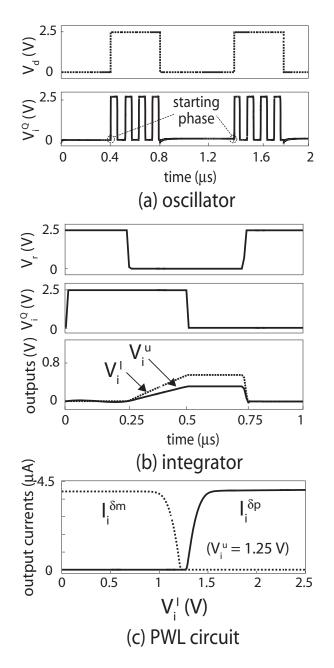

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>                                                                     | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109<br>110<br>112                                  |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul>                                                                                  | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109<br>110<br>112                                  |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> </ul>                                                        | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109<br>110<br>112                                  |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>                                                                     | Definition of single learning cycle                                                  | 107<br>108<br>109<br>109<br>110<br>112<br>5<br>113                      |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> </ul>                                           | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>113<br>114                      |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ul>                             | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>113<br>114                      |

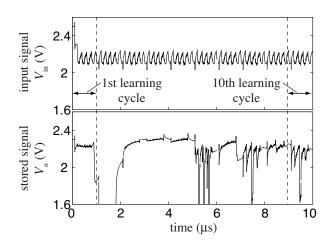

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ul>                             | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>1113<br>114<br>115              |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> </ul>               | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>113<br>114<br>115<br>116        |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> <li>7.12</li> </ul> | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>113<br>114<br>115<br>116        |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> <li>7.12</li> </ul> | Definition of single learning cycle                                                  | 107<br>108<br>109<br>110<br>112<br>5<br>113<br>114<br>115<br>116<br>117 |

| 7.14 | Simulation results of circuit network with $N = 20$ ; (a) timing         |

|------|--------------------------------------------------------------------------|

|      | chart, (b) time evolution of $i$ -th integrator outputs and (c) evo-     |

|      | lution of weight voltages                                                |

| 7.15 | Evolution of temporal input sequence $V_{\rm in}$ and learned output se- |

|      | quence $V_u$ (first to 10th learning cycles)                             |

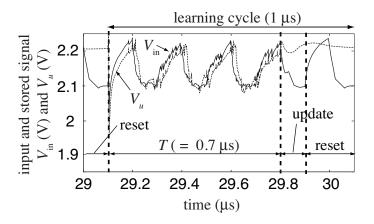

| 7.16 | Temporal input sequence $V_{\rm in}$ and learned output sequence $V_u$   |

|      | after 29th learning cycle                                                |

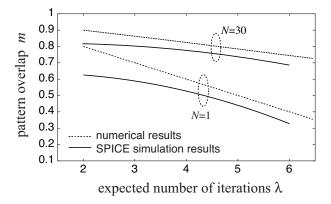

| 7.17 | Numerical and SPICE results showing pattern overlaps between             |

|      | input and output sequences for different $Ns$ and complexity of          |

|      | input sequence $\lambda$                                                 |

10

## Chapter 1

## Introduction

This research is centered on the study, design and implementation of Neural elements, like neurons and networks of neuron. More specifically, the implementation of neural elements involved in the processing of sensory information. The implementation of such kind of systems is usually referred to as "Neuromorphic systems". It is consist of "simple circuits" inspired by the organizing principles of animal neural systems and implemented using standard Complementary Metal-Oxide Silicon (CMOS) technology. This chapter give an introduction to basic terminology and concepts necessary to have an idea of how the biological sensory system processed information.

### 1.1 Background

Research into neuromorphic systems is part of the large field of computational neuroscience. The era of neural networks is believed to begin in 1943 with the work of McCulloch and Pitts [1], where they proposed that brain cells (neurons) could be modeled by a "simple electronic circuit". During the next fifteen years there was considerable work on detailed logic of threshold networks. In 1958 Frank Rosenblatt introduced his architecture for classification. In 1982, John Hopfield published a paper describing the Hopfield network [2], a simple artificial network which is able to "store" certain patterns.

However, the term "neuromorphic" appears to have started off meaning neuron-like in the late 1980's particularly by those interested in optical implementation of neural networks. The meaning of the word is mimic(ing) specific neurobiological functions, and the meaning seems to have come from the silicon implementation side from the work of mainly two research groups; Alspector's group [3] and Mead's group [4] [5].

The earliest neuromorphic systems were concerned with providing an engi-

neering approximation to some aspects of **sensory systems** such as, auditory system [6] and visual system [7]. More recently, there has also been work on robot control systems, on modeling various types of neurons, and on including adaptations in hardware systems.

Although the detailed information of the brain operation still a puzzle to be solve by neuroscientists, the knowledge that has been accumulated through the biological neural networks research, does give good clues toward the construction of artificial systems that **emulate** some of the characteristic of the nervous system. Biological neural networks provide us with resourceful guidance on building the intelligent machine and to pursue the "brain building". In addition, the progress in hardware implementation will contribute to a better understanding of paradigms and biological systems as well as many useful applications.

Therefore, based on current knowledge of biological systems, this work aims to develop basic neural circuits and networks that emulate characteristics of the processing of information carried-out by the biological sensory system. As known, the sensory system is the part of the nervous system responsible for the processing of sensory information, it consists of sensory receptors, neural pathways, and other parts of the brain involved in sensory perception. This thesis focus mainly in two areas of the sensory processing; the early sensory processing, including receptors and synapses; and the cognitive sensory processing.

### 1.2 Objective

This research is focus on the design and hardware implementation of biological systems, particularly in the human brain. The human brain is a complex, nonlinear and highly parallel system. Moreover, the brain can easily adjust to a new environment by "learning" and it can deal with information that is fuzzy, noisy or inconsistent. Owing to these characteristics, understanding how the brain works, in particular, how it extracts useful information from "noisy" neural signals, has been one of the most challenging tasks in neuroscience.

With the success of digital systems nowadays, one may ask, what alternative ways of exploring microelectronics are in there?. The answer is simple, the human brain outperforms any computer or supercomputer, not only in size, but also in "efficiency" and robustness. Moreover, the brain can adjust to a new environment by "learning" and it can deal with information that is probabilistic and noisy.

Digital computers of today solve a problem by imposing a computational recipe, or algorithm, on general purpose hardware. So unless the specific steps that a computer needs to follow are known the computer can not solve the problem. Neuromorphic systems by contrast, embody in the physical behavior of their circuits "analogues" of the processes performs by neural systems. They exhibit fundamental neural functions because the structure of the nervous systems are reproduce on silicon chip. In other words, they transfer our knowledge of neuroscience into practical devices that can interact directly with the real world in the same way that biological neural systems do.

Although the detailed information of the brain operation still a puzzle to be solve by neuroscientists, the knowledge that has been accumulated through the biological neural networks research, does give good clues toward the construction of artificial systems that emulates some of the characteristic of the nervous system.

To this end, based on current knowledge of biological sensory systems, this thesis aims to implementing basic circuits that emulate some basic characteristics of sensory systems; detection of weak and noisy input stimuli, synchronization, properties of synaptic connections, separation or decomposition of natural scenes, and storage of temporal sequences.

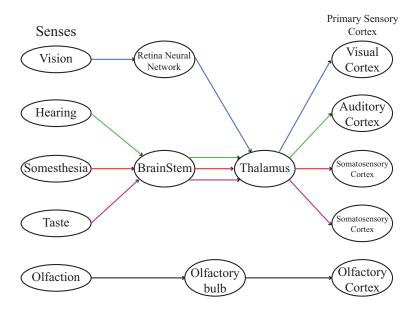

The sensory system is a part of nervous system responsible processing sensory information. The sensory system informs areas of the cerebral cortex of changes that are taking place within the body or in the external environment. It consists of sensory receptors that receive stimuli from internal and external environment, neural pathways that conduct this information to the brain, and parts of the brain that process this information. Figure 1.1 shows a schematic of the different senses (from visual to olfaction) and the route they follow to transfer the input stimulus to their respective area in the cortex [8].

#### Receptors

Receptors are specialized endings of afferent neurons (sensory neurons) or separate cells that affect ends of afferent neurons. They collect information about external and internal environment in various energy forms (stimulus). Stimulus energy is first transformed into nerve impulses (electrical pulses) or receptor potentials by a process called stimulus transduction.

Sensory receptors respond to specific stimulus modalities. Some of them are:

- Thermoreceptors, respond to change in the temperature.

- Photoreceptors, respond to light.

- Mechanoreceptors, detect changes in pressure, position, or acceleration.

- Chemoreceptors, detect certain chemical stimuli.

Figure 1.1: Route followed by the different inputs of the sensory system.

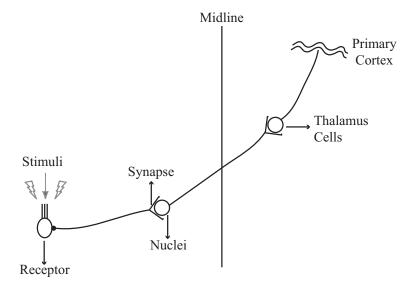

Figure 1.2: General outline of the ascending pathway.

#### Neural pathway

The sensory or ascending pathway is the route followed by a sensory nerve impulse from a receptor to the brain. Figure 1.2 is a schematic showing the general outline of the ascending pathway. The sensory neurons (that form the ascending pathway) are activated by input stimulus detected and transformed by the sensory receptors (specialized end of the sensory neurons). The active neurons then convey the information to their respective nuclei in the central nervous systems, where the information is further processed as it progress via sensory systems to the cerebral cortex.

The sensory pathway for, the visual, hearing and somesthesia senses are interrupted by synaptic transmission in the ventral thalamus, and the axon of these neurons project to regions of the cerebral cortex that are specific to each sense, and are known as the primary sensory cortices (Fig. 1.1). From there information progresses to secondary and association cortices. The fibers of the taste pathway, after making synaptic connections with cells in the brainstem projects not only to the ventral thalamus, but it also projects to other areas such as, Limbic system, motor pathways and pancreas. The cells in the thalamus project to the insular cortex and somatosensory areas.

The olfactory pathway reaches parts of the central nervous systems that are different from those of the four other senses. After reaching the olfactory bulb, where the first synapse is located, it projects to: anterior olfactory nucleus, Piriform cortex, medial amygdala and entorhinal cortex.

Following the basic characteristic of the biological sensory processing from stimuli reception to processing (sensory pathway) this thesis is outlined as follows:

- Chapter 1 explains the introduction, background and purpose of this research

- Chapter 2 gives an introduction to the basics of neural networks and neuromorphic systems and a brief explanation of CMOS circuits used in this research.

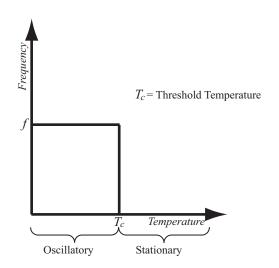

- Chapter 3 starts with the implementation of a circuit for the first step of sensory perception "receptors"; *A temperature receptor*. The model is inspired by the operation of **excitable sensory neurons**. The circuit consists of sub-threshold CMOS circuits whose dynamical behavior changes at a given threshold temperature, *i.e.*, switches to and from oscillatory and stationary. The threshold temperature is set to a desired value by adjusting an external bias voltage. The operation of the model was

studied in detail through theoretical analysis, extensive simulations, and experimentally through discrete MOS devices.

- Chapter 4 introduces a network model exhibiting array-enhanced stochastic resonance, for detection of weak input signal (stimuli). Sensory systems are expose to the noise in the environment and to the noise inherit in their own elements. Therefore, neural systems may employ different strategies that can exploit the properties of noise to improve the efficiency of neural operations. This chapter focuses on the implementation of such kind of noise driven networks in hardware. The model consists of a 2D grid network in which all elements (neuron) accept a common sub-threshold input. In addition, no external noise source is required for the operation of the network as each neuron interact with other neurons through the coupling to generate spatio-temporal noises.

- Chapter 5 introduces a depressing synapse model. Moreover, the dynamical effects of depressing synapses on synchronization are studied using a simple network of neurons. The model was studied through circuits simulations using a simulation program with integrated circuit emphasis (SPICE). Consequently, timing jitter among neurons was significantly reduced when using depressing synapse as compared to non-depressing synapses.

In chapters 6 and 7, the focus is shifted to the cognitive processing area. Two model are introduced; a neural segmentation model, and a model for the storage of temporal sequences. Therefore, the following chapters are distributed as follow:

- In chapter 6 it is proposed a neural network model for sensory segmentation. Segmentation is refer to the ability to decompose natural scenes into coherent "segments" (each segment corresponds to a different component of the scene). The model consists of neural oscillators mutually coupled through synaptic connections. The model performs segmentation in temporal domain, which is equivalent to segmentation according to the spike timing difference of each neuron. Thus, the learning is governed by symmetric spike-timing dependent plasticity (STDP). The basic operations of the proposed model was studied numerically and with circuit simulations using a simulation program with integrated circuit emphasis (SPICE).

- Chapter 7 presents a model for learning and recalling the temporal input stimuli. The model consists of neural oscillators which are coupled to a common output cell through positive or negative synaptic connections. The basic idea is to learn input sequences, by superposition of rectangular

periodic activity (oscillators) with different frequencies, by strengthened (or weakened) the weights of synaptic connections when the output of oscillatory cells overlap (or do not overlap) with the input sequence. The operation of the model was numerically confirmed. Moreover, fundamental circuit operations were studied and the operations of the circuit network was confirmed through SPICE simulations.

• Finally, chapter 8 concludes this research.

## Chapter 2

# Basic concepts CMOS circuits and neural networks

This chapter will give a brief explanation of basic circuits and terminology necessary for the understanding of this work. Its start with the explanation of CMOS circuit structure, follow by the explanation of basic circuitry used for implementing the different sensory systems described in this thesis. In addition, the terminology used in the study of artificial and biological neural networks is explained.

### 2.1 CMOS circuits

In today's integrated circuits (IC) industry a good understanding of semiconductors devices is essential. In special the MOS transistor (MOSFET) that has become the most used semiconductor device today. Since late 1970's the MOS-FET has been extremely popular, this is because, compared to other transistors they can be quite small and their manufacturing process is relatively simple. Furthermore, digital logic and analog designs can be implemented with circuits using only MOSFETs devices. They can be used as the building blocks of logic gates, fundamental in the design of digital circuits like microprocessors, in which transistors act as on-off switches. For analog circuits transistors respond to a continuous range of inputs with a continuous range of outputs. For these reasons, most very-large-scale integration (VLSI) circuits are made using MOS technology.

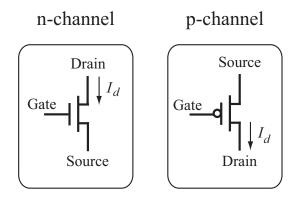

Figure 2.1: Symbols used to denote the MOSFET devices.

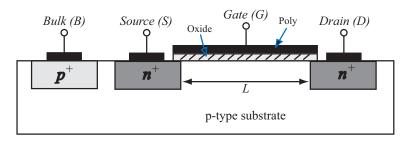

Figure 2.2: Simplified structure of an n-channel MOSFET.

### 2.1.1 The MOSFET

### Symbology

Before explaining the operation of MOSFET, lets consider the symbology used to denote the devices. Figure. 2.1 shows the symbols used for a n-type and p-type MOSFET. It is important to note that a MOSFET is a four-terminal device, the symbols shown in the figure are the simplified model in which the bulk is connected to the source.

### Structure

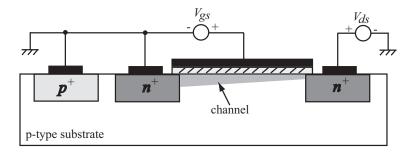

Figure 2.2, shows a simplified structure of an n-channel MOSFET (nMOS). The device is fabricated on a p-type substrate (also called "body"), it consists of two heavily doped n regions that form the source and the drain terminals, a thin layer of silicon dioxide ( $SiO_2$ ) is insulating the gate from the substrate. Polysilicon (poly) operating as the gate terminal is deposited on top of the oxide.

It is important to note that the substrate forms pn junctions with the source and the drain regions. Since the drain will be at a positive voltage relative to the source (reverse-biased), the two pn junctions can be cut off by connecting the bulk terminal to the source.

Figure 2.3: a) Structure of an nMOS transistor with gate voltage  $V_{gs}$ , b) corresponding symbology, and c) nMOS showing the depletion capacitance.

The structure of pMOS devices can be obtained by inverting all of the doping types. In practice nMOS and pMOS devices are fabricated on the same wafer, i.e., the same substrate. For this, one device type can be placed in a local substrate called "well".

### Operation and I/V characteristic

Lets consider the Fig. 2.3 (a) the nMOS with the gate connected to an external voltage  $V_{gs}$ . The corresponding symbology is shown in Fig. 2.3(b). Since the gate and the substrate form a capacitance, when  $V_{gs}$  becomes more positive, holes in the *p*-substrate are repelled from the gate area however, for small  $V_{gs}$ , the voltage is not positive enough to attract a large number of electrons creating a depletion region. Under this condition, no current flows. When  $V_{gs}$  increases, the width of the depletion region also increase. At this point, the structure resembles two capacitors in series,  $C_{cox}$  and  $C_{dep}$  as shown in Fig. 2.3 (c). The increase on  $V_{gs}$  also attracts electrons from the  $n^+$  regions (source and drain) where they are abundant. Thus, a "channel" of charge carriers is formed under the gate oxide and the transistor is "turned on" as shown in Fig. 2.3 (a). The value of  $V_{gs}$  for which this occurs is called "threshold voltage" ( $V_{th}$ ).

Now lets consider the voltage  $V_{ds}$ , shown in Fig. 2.3 (a). This voltage causes a current  $I_d$  to flow from drain to source. The magnitude of  $I_d$  depends on the density of electrons in the channel, and the density of electrons depends on the magnitude of  $V_{gs}$ . When  $V_{gs} = V_{th}$  the channel is just formed, so the current is

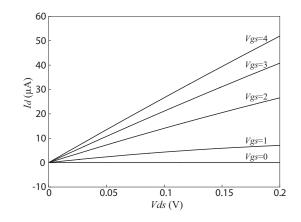

Figure 2.4:  $I_d$  -  $V_{ds}$  characteristic of an nMOS. ( $V_{ds}$  is small)

Figure 2.5: nMOS transistor channel after applying  $V_{ds}$

still very small. When Vgs exceeds  $V_{th}$ , the channel charge density increases, (the channel's width increases). As a result, the conductance of the channel increases. The conductance of the channel is proportional to the *effective* voltage  $(V_{gs} - V_{th})$ . The current  $I_d$  is proportional to this voltage  $(V_{gs} - V_{th})$ and to the voltage  $V_{ds}$  that causes  $I_d$  to flow. Figure 2.4 shows the  $I_d - V_{ds}$ characteristic of an nMOS transistor, with small  $V_{ds}$  for various values of  $V_{gs}$ . It can be observed that the MOSFET operates as a linear resistance whose value is controlled by  $V_{gs}$ . When  $V_{gs}$  is small, the resistance is big, and as  $V_{gs}$ increases the resistance decreases.

The channel's width depends on voltage  $V_{ds}$ , therefore, when  $V_{ds}$  increases the potential of the channel at the drain decreases  $(V_{gs}-V_{ds})$ . It can be observed in Fig. 2.5, that the channel is not longer uniform. If  $V_{ds}$  keep increasing, the channel reduces more and more and its resistance increases correspondingly. Eventually, when the channel potential at the drain is reduce to  $V_{th}$   $(V_{gs}-V_{ds} = V_{th})$  the channel width is almost zero, and the channel is said to be "pinched off".

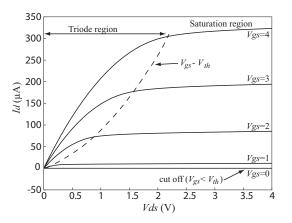

Figure 2.6 shows the  $I_d$  -  $V_{ds}$  characteristic of an nMOS transistor. From

Figure 2.6:  $I_d$  -  $V_{ds}$  characteristic of an nMOS transistor.

there it can be indicated three regions of operation; the "cut of f" region (also called *sub-threshold* or *weak inversion* region), the "triode" or *linear* region and the "saturation" region. The saturation region is used for the MOSFET to operates as an amplifier, for the operation as a switch, the cut off and the triode regions are used.

The MOSFET is cut off when  $V_{gs} < V_{th}$ . To operate in the triode region  $V_{gs}$  should be higher than  $V_{th}$  ( $V_{gs} \ge V_{th}$ ) and  $V_{ds}$  should be kept small enough ( $V_{gs} - V_{ds} > V_{th}$ ) so that the channel remains continuous.

In the triode region the  $I_d$  -  $V_{ds}$  characteristic can be describe by:

$$I_d = \beta [(V_{gs} - V_{th})V_{ds} - \frac{V_{ds}^2}{2}]$$

(2.1)

where  $\beta$  is the transconductance parameter given by:

$$\beta = K P_n \frac{W}{L}.\tag{2.2}$$

If  $V_{ds}$  is very small  $(V_{ds} \ll 2(V_{gs} - V_{th}))$ , Eq. (2.1) can be expressed as:

$$I_d = \beta (V_{gs} - V_{th}) V_{ds} \tag{2.3}$$

this linear relationship represents the operation of the MOS transistor as a linear resistor as shown in Fig. 2.4, with resistance  $R_d$ :

$$R_d = \frac{V_{ds}}{I_d} = [\beta(V_{gs} - V_{th})]^{-1}$$

(2.4)

whose value is control by  $V_{gs}$ .

The MOSFET operates in the saturation region when  $V_{qs}$  is grater than  $V_{th}$

Figure 2.7:  $I_d$  -  $V_{gs}$  characteristic of an nMOS transistor.

Figure 2.8:  $I_d$  -  $V_{ds}$  characteristic of an nMOS transistor operating in the sub-threshold region.

and the drain voltage  $V_{ds}$  does not fall below the gate voltage  $V_{gs}$  by more than  $V_{th}$ ,  $(V_{ds} \ge V_{gs} - V_{th})$ . The saturation current can be expressed as:

$$I_d = \frac{\beta}{2} (V_{gs} - V_{th})^2.$$

(2.5)

In saturation the drain current  $I_d$  is independent of the drain voltage  $V_{ds}$ , instead is determined by the gate voltage  $V_{gs}$ . Figure 2.7 show the  $I_d$  -  $V_{gs}$ characteristic of an nMOS transistor. Thus, the MOSFET in saturation behaves as a current source whose value is controlled by  $V_{gs}$ .

### 2.1.2 Sub-threshold current

The current that flows when  $V_{gs} < V_{th}$  is called sub-threshold, current. The MOSFET is said to be operating in the *weak inversion*, *cut off* or *sub*-

*threshold* region. This current is due to diffusion current between the drain and the source and is given by:

$$I_d = I_0 e^{V_g/\eta V_T} (e^{-V_s/V_T} - e^{-V_d/V_T})$$

(2.6)

where  $\eta$  is the slope factor,  $V_T$  is the thermal voltage  $(V_T = kT/q)$ , k is the Boltzmann's constant, T is the temperature, and q is the elementary charge. Current  $I_0$  is given by:

$$I_0 = 2\eta \beta V_T^2 e^{-V_{th}/\eta V_T}$$

(2.7)

For small  $V_{ds}$  the transistor operates in the *triode region* (also called *linear region*) described by Eq. (2.8). In terms of  $V_{ds}$  this equation can be rewritten as:

$$I_d = I_0 e^{V_{gs}/\eta V_T} (1 - e^{-V_{ds}/V_T})$$

(2.8)

As  $V_{ds}$  increases  $(V_d > 4V_T)$  the transistor operates in saturated region. The *I-V* relation in this region is described by:

$$I_d = I_0 e^{(V_g - V_s/\eta V_T)}$$

(2.9)

Figure 2.8 shows the Id- $V_{ds}$  characteristic of a transistor operating in the saturation region.

### 2.1.3 Sub-threshold analog circuits

Since early 1980s, digital signal processing were becoming more powerful. The advance in IC technology provided compact, efficient implementation of circuits, so, many functions that were realized in the analog form were easily performed in the digital domain. However, in the past two decades, CMOS Technology has rapidly embraced the field of analog integrated circuits, providing low-cost, high-performance, rising this way the use of analog circuits. In addition, by careful use o the analog characteristics of transistors, arithmetic functions such as, addition, multiplication, exponential, logarithmic and tanh functions may be implemented using relatively few transistors as compare with digital circuits. Consequently, analog circuits have been proved fundamentally necessary for solving complex tasks, including the processing of natural stimuli. This chapter gives a brief explanation of commonly used analog circuits, including the current mirror, the differential pair and the transconductance amplifier.

Figure 2.9: Current mirror circuit.

Figure 2.10: Current mirror simulation results.

### Current mirror

The basic circuit of a current mirror is shown in Fig. 2.9. First lets us suppose that the two nMOS are identical. A current  $I_1$  flows through transistor  $m_1$ , corresponding to the gate voltage,  $V_{gs_1}$ . Since the gates of  $m_1$  and  $m_2$  are connected, the gate voltage of  $m_2$  is the same as the gate voltage of  $m_1$ ,  $(V_{gs_1} = V_{gs_2} = V_{gs})$ . Ideally the same current that flows through  $m_1$ , flows through  $m_2$ . In other words, two identical MOS devices with equal gate voltages and operating in saturation carry equal currents.

The current  $I_1$  is given by:

$$I_1 = I_{01} e^{(V_{gs_1})/\eta V_T}.$$

(2.10)

while the output current  $I_2$  is:

$$I_2 = I_{02} e^{(V_{gs_2})/\eta V_T}.$$

(2.11)

Figure 2.11: Schematic of the differential pair.

Since  $V_{gs_1} = V_{gs_2}$  and  $I_0 \propto \beta$  (Eq. (2.7)) the ratio of the currents can be written as:

$$\frac{I_2}{I_1} = \frac{\beta_2}{\beta_1} = \frac{W_2 L_1}{W_1 L_2} \tag{2.12}$$

This equation shows how to adjust the W/L ratio of the two devices to achieve the desired output current. By making  $L_1 = L_2$ , Eq. (2.12) is simplified as:

$$\frac{I_2}{I_1} = \frac{W_2}{W_1} \tag{2.13}$$

SPICE simulation results are shown in Fig. 2.10.

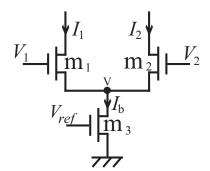

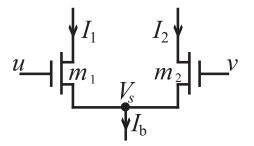

### Differential pair

The differential pair is one of the basic amplifying stages in amplifier design. The differential pair's output is represented as the difference between the voltage of its inputs. The differential pair circuit is shown in Fig. 2.11. It consists of tree nMOS transistors. Transistor  $m_3$  is used as a current source. Normally the drain voltage V is large enough so that the drain current  $I_b$  is saturated and its value is controlled by the bias voltage  $V_{ref}$ . The current  $I_b$  is divided between transistor  $m_1$  and  $m_2$  depending on their gate voltages  $V_1$  and  $V_2$ .

$$I_b = I_1 + I_2 \tag{2.14}$$

As explained in the previous sections, the saturated drain current is given by Eq. (2.8). Applying this expression to the current of transistors  $m_1$  and  $m_2$ (Fig. 2.11)

$$I_1 = I_0 e^{\kappa (V_1 - V)/V_T}$$

(2.15)

$$I_2 = I_0 e^{\kappa (V_2 - V)/V_T}$$

(2.16)

Figure 2.12: Differential pair output currents as function of  $V_1 - V_2$ .

So  $I_b$  can be expressed as:

$$I_b = I_0 e^{-V/V_T} \left( e^{\kappa(V_1)/V_T} + e^{\kappa(V_2)/V_T} \right)$$

(2.17)

Solving the equation:

$$e^{-V/V_T} = \frac{I_b}{I_0} \frac{1}{(e^{\kappa(V_1)/v_T} + e^{\kappa(V_2)/v_T})}$$

(2.18)

Substituting this expression in Eqs. (2.15) and (2.16) it is obtained:

$$I_1 = I_b \frac{e^{\kappa(V_1)/V_T}}{(e^{\kappa(V_1)/V_T} + e^{\kappa(V_2)/V_T})}$$

(2.19)

$$I_2 = I_b \frac{e^{\kappa(V_2)/V_T}}{(e^{\kappa(V_1)/V_T} + e^{\kappa(V_2)/V_T})}$$

(2.20)

If  $V_1$  is higher than  $V_2$ , transistor  $m_2$  is off, and all the current goes through  $m_1$ ,  $(I_1 \approx I_b)$ . The contrary is also true. Currents  $I_1$  and  $I_2$  as function of  $V_1 - V_2$  are shown in Fig. 2.12.

Equations (2.19) and (2.20) can be expressed in terms of voltage difference  $(V_1 - V_2)$  by subtracting them:

$$I_1 - I_2 = I_b \left(\frac{e^{\kappa(V_1)/V_T} - e^{\kappa(V_2)/V_T}}{e^{\kappa(V_1)/V_T} + e^{\kappa(V_2)/V_T}}\right)$$

(2.21)

Then by multiplying and dividing by  $e^{-(V_1+V_2)/2}$ , it is obtained

$$I_1 - I_2 = I_b \left(\frac{e^{\kappa(V_1 - V_2)/2V_T} - e^{-\kappa(V_1 - V_2)/2V_T}}{e^{\kappa(V_1 - V_2)/2V_T} + e^{-\kappa(V_1 - V_2)/V_T}}\right)$$

(2.22)

Figure 2.13: Transconductance amplifier, a)schematic, b) symbol.

Figure 2.14: Transconductance amplifier output current

The r.h.s. of this equation can be express as tanh:

$$I_1 - I_2 = I_b \tanh \frac{\kappa (V_1 - V_2)}{2V_T}$$

(2.23)

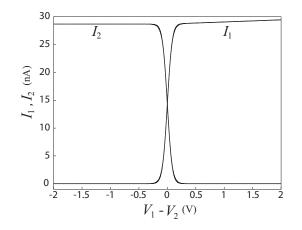

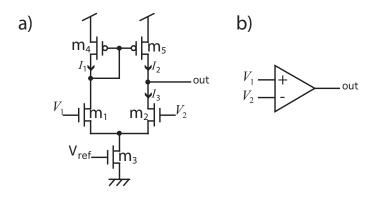

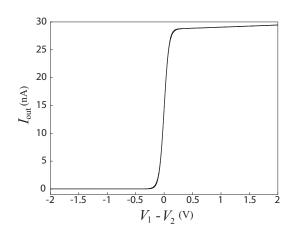

### Transconductance amplifier

The schematic of the transconductance amplifier is shown in Fig. 2.13 (a). The amplifier's symbol is shown in Fig. 2.13 (b). The circuit consists of a differential pair  $(m_1 - m_2 - m_3)$  and a current mirror  $(m_4 - m_5)$ . Current  $I_1$  is copied to  $I_2$  by the current mirror. Thus, the output current will be the subtraction of the currents  $(I_2 - I_3)$ .

The output current of a simple amplifier is shown in Fig. 2.14. The curve is very close to a (tanh) as expected, from the explanations of differential pairs circuits in the previous subsection.

### 2.2 Introduction to neural networks

Building intelligent systems to mimic biological systems, in particular neural systems has capture the attention of the world for years. So, it is not surprising that a technology such as neural networks has generated great interest. The human brain is a complex, non-linear and highly parallel system (it can process incoming stimuli simultaneously) that can easily outperform any existing computer. The brain has many features desirable in artificial systems:

- The brain is flexible. It can adjust to new environment by "learning".

- It is robust and fault tolerant. Nerve cell die every day without affecting its performance significantly.

- it is non-linear and highly parallel.

- It can deal with information that is fuzzy, probabilistic, noisy or inconsistent.

The advantage of parallel processing is that it allows the brain to simultaneously identify different stimuli which in consequence allows for quick and decisive actions. The brain can solve complex problems that are hardly approachable with traditional computers. A good example is the processing of visual information, even a baby is much better and faster at recognizing objects, faces, etc., than the most advance computer. While the computer's speed is a million times faster than a human's neural network, the brain have a large number of processors compared to computers.

Biological neural networks provide the best source of knowledge for developing powerful engineering neural networks.

### 2.2.1 Neurons

The brain contains many billions (about  $10^{11}$ ) of nerve cells or "neurons". Neurons are organized into a very complicated intercommunicating network. Typically each neuron is physically connected to tens of thousands of others neurons. Using these connections neurons can pass electrical signals between each other.

Individual neurons are complicated. They have a myriad of parts, subsystems, and control mechanisms. There are over one hundred different classes of neurons, depending on the classification method used. The artificial neural networks try to replicated the most basics elements of this complicated and powerful organism.

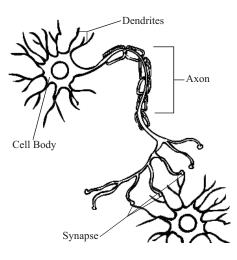

Figure 2.15 shows the schematic of a typical and simple neuron. The cell body or soma is the central part of the neuron, connected to the cell body are

Figure 2.15: Typical neuron.

the dendrites, cellular extensions with many branches, and metaphorically this overall shape and structure is referred to as a dendritic tree. This is where the majority of input to the neuron occurs. Extending from the cell body is the axon, a finer, cable-like projection, which eventually arborizes into strands and substrands. The axon carries nerve signals away from the cell body. The axon terminal contains synapses or synaptic junctions transmitting the signal to other neuron's dendrites or cell bodies.

The transmission of a signal from one cell to another at a synapse is a complex chemical process, in which ion channels allow ions (sodium  $Na^+$ , calcium  $Ca^+$ , and chloride  $Cl^-$ ) to move into and out of the cell. Ion channels control the flow of ions across the cell membrane by opening and closing in response to voltage changes and both internal and external signals. The membrane potential is the difference in electrical potential between the interior of a neuron and the surrounding extracellular medium. Current flowing into the cell changes the membrane potential to less negative or more positive values. If the membrane potential rises above a threshold level, a positive feedback process is initiated, and the neuron generates an action potential of fixed strength and duration. It is said then that the cell has "fired". After firing, the cell has to wait for a time called "refractory period" before it can fire again. For more information refer to [9]

## 2.2.2 Artificial neural networks

As mention in the previous section, the brain contains billions of neurons. Each neuron is connected to thousands of others neurons. Through these connections

Figure 2.16: Basic artificial neuron.

(synapses) neurons can pass electrical signal between each other. These synaptic connections have varying strength which allows the influence of a given neuron on one of its neighbors to be strong, weak or just do nothing. Many aspects of brain function, particularly the learning process, are closely associated with the adjustment of these connections strengths. Brain activity is then represented by particular patterns of firing activity among this network of neurons. So, it is this simultaneous cooperative behavior of many simple processing units the source of the enormous computational power of the brain.

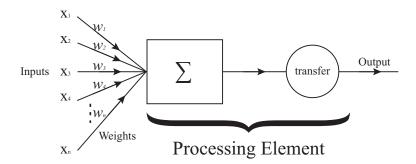

Artificial neural networks are electronic models based on the neural structure of the brain. Neural networks consists of many simple processing elements (PE) and weighted connections. These processing elements operate in parallel to solve specific problems. Their functions are determined by the networks structure, connections strengths and the processing performed by each element.

Neural networks can be though as devices that accept inputs and produce outputs. Basically, a biological neuron receives inputs from other sources through synapses of other neurons, then the soma combines them in some way, performs a generally non-linear operation on the result and finally outputs the final result through the axon and the synapse. Even when there are many variations of neuron, all natural neurons have the same four basic components. An artificial neuron simulate the four basic functions of a natural neuron. Figure 2.16 shows a fundamental representation of an artificial neuron.

In the model shown in Fig. 2.16, various inputs to the neuron are represented by  $X_i$  (i = 0, 1, ..., n). Each of these inputs are multiplied by a connection weight  $w_i$ . In the simplest case, these products are summed, and pass through a transfer function to generate the result, and then the output. This electronic implementation is possible with other networks structures which utilize different summing functions as well as different transfer functions.

#### Connections

The weights  $w_i$  in Fig. 2.16 for (i = 0, 1, ..., n) represent the strength of the synaptic connections from neuron *i*th. The connections define the flow through the network and modulates the amount of information passing between to the processing element.

Connections weights are adjusted during the learning process that capture the information. Connections weights that have positive values are "excitatory" connections. Connections weights with negative values are "inhibitory" connections. And those connections with a zero value are the same as not having connections present. By allowing a subset of all the possible connections to have nonzero values, sparse connectivity between processing elements (PEs) can be stimulated, because it is often desirable for a PE to have a internal bias value (threshold value).

## **Processing elements**

The PE is the portion of the neural network where all the computing is performed. There are two important qualities that a PE must possess:

- PEs require only local information. The information necessary for a processing element to produce an output value must be present at the inputs and resides within the PE.

- PEs produce only one output value.

These two qualities allow neural networks to operate in parallel. Mathematically, the output of a PE is a function of its inputs and its weights.

$$Y = F(X, w_i). \tag{2.24}$$

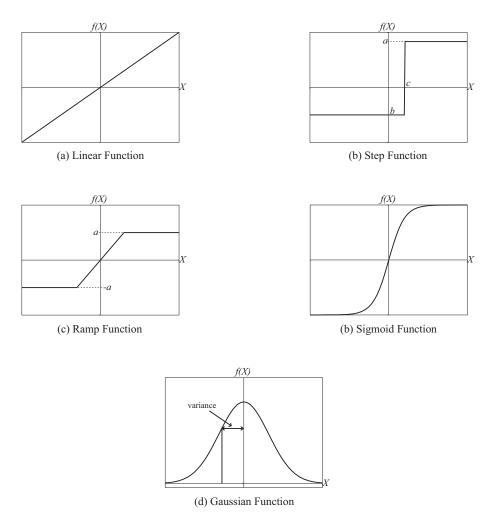

## 2.2.3 Processing elements transfer function

PEs transfer functions, also referred as activation functions can change the behavior of the network. Although the number of PE transfer functions possible is infinite, five are regularly employed by the majority of neural networks:

- Linear function

- Step function

- Ramp function

- Sigmoid function

- Gaussian function

Figure 2.17: Processing elements (PE) transfer functions.

With the exception of the linear function, all of these functions introduce a nonlinearity in the network dynamics by bounding the output value within a fixed range. Each function is shown in Fig. 2.17 (a-e).

## Linear function

The linear function Fig. 2.17 (a), produces a linear output from the input X according to:

$$f(X) = \alpha X \tag{2.25}$$

where the X ranges over the real numbers and  $\alpha$  is a positive scalar. If  $\alpha = 1$  is equivalent as removing the transfer function.

#### Step function

The step function Fig. 2.17 (b) it produces two values a and b. If the input X is higher than a predefined value c (threshold value) the function produce the value a; otherwise will produce the value b, where a and b are scalars.

$$f(X) = \begin{cases} a, & \text{if } x \ge c \\ b, & \text{if } x \le c \end{cases}$$

(2.26)

A particular step function, the "unit step function" or "Heaviside step function" is a discontinuous function whose value is zero for negative argument and one for positive argument

$$f(X) = \begin{cases} 1, & \text{if } x \ge 0\\ 0, & \text{otherwise} \end{cases}$$

(2.27)

this kind of functions is common in neural networks, and have been implemented in models like the McCulloch and Pitts [1], and the Hopfield neural network [2].

## Ramp function

The ramp function Fig. 2.17 (c). It can be though as a combination of the step function and the linear function. The functions has an upper and a lower bound and posses a linear response between the bounds.

$$f(X) = \begin{cases} a, & \text{if } X \ge a \\ X, & \text{if } |X| < a \\ -a, & \text{if } X \le a \end{cases}$$

(2.28)

#### Sigmoid function

The sigmoid function Fig. 2.17 (d). Is a continuous version of the ramp function. Is a mathematical function that produces a sigmoid curve (S-shape curve). Sigmoid functions are often used in neural networks to introduce nonlinearity in the model and/or to bound signals to within a specified range. A popular neural net element computes a linear combination of its input signals, and applies a bounded sigmoid function to the result; this model can be seen as a "smoothed" variant of the classical threshold neuron.

$$f(X) = \frac{1}{1 + e^{-\alpha X}}$$

(2.29)

where  $\alpha > 0$  provides an output from 0 to 1. It is important to note that there is a relationship between Eq. 2.27 and Eq. 2.29. When  $\alpha = \infty$  in Eq. 2.29, the slope of the sigmoid function between 0 and 1 become step, and in effect become the Heaviside function.

Two alternatives to the sigmoid functions are the hyperbolic tangent

$$f(X) = tanh(X) \tag{2.30}$$

which ranges from -1 to 1, and the augmented ratio of squares

$$f(X) = \begin{cases} \frac{X^2}{1+X^2}, & \text{if } x > 0\\ 0, & \text{otherwise} \end{cases}$$

(2.31)

which ranges from 0 to 1.

Sigmoid functions are very suitable for implementation in analog VLSIs because they can be implemented by using differential-pair circuits.

## Gaussian function

The gaussian function Fig. 2.17 (e). Is a radial function that requires a variance value v > 0.

$$f(X) = \alpha e^{-\frac{(X-b)^2}{v}}$$

(2.32)

where  $\alpha$  is the height of the Gaussian peak, b is the position of the center of the peak, and v is the variance which controls the width of the "bump".

## 2.2.4 Learning

Learning is one of the most important features on neural networks. Since all knowledge is encode in weights, "learning" is define as a change in connection weight values.

On the network level, a weight represents how frequent the receiving unit has been activated simultaneously with the sending unit. Hence, weight change between two units depends on the frequency of both neurons firing simultaneously. In other words, the weight between two neurons will increase if the two neurons activate simultaneously; it is reduced if they activate separately. This form of weight change is called "*Hebbian learning*" [10], which provides a simple mathematical model for synaptic modification in biological networks. Its most general form is expressed as:

$$\Delta w_{i,j} = x_i x_j \tag{2.33}$$

or the change in the *i*th synaptic weight  $w_{i,j}$  is the product of the output of unit *i* and unit *j*. Several modifications but the basic principle still accepted.

There are several ways of learning techniques. The most important are:

- Supervised Learning

- Unsupervised Learning

- Reinforcement Learning

#### Supervised learning

Supervised learning is a process that incorporates an external teacher, it requires sample input-output pairs from the function to be learned, the data are available and are used to calculate weight change. In other words, supervised learning requires a set of questions with the right answers.

Supervised learning is further classified into two subcategories: structural learning and temporal learning. Structural learning is concerning with finding the best possible input/output relationship for each individual pattern pair. Temporal learning is concerned with capturing a sequence of patterns necessary to achieve some final outcome. In temporal learning, the current response of the network is dependent on previous inputs and responses.

### Unsupervised learning

Unsupervised learning, also called self-organization, is a process that does not require external teacher, it relies upon local information during the entire learning process. Unsupervised learning organizes presented data and discovers its emergent collective properties. Examples of unsupervised learning include, Hebbian learning and competitive learning.

## 2.3. SUMMARY

#### **Reinforcement learning**