# 極低電力 LSI のための間欠パルス回路

松下 拓道 † 上野 憲一 † 浅井 哲也 † 雨宮 好仁 †

†北海道大学工学部 〒060-0814 北海道札幌市北区北 14 条西 9 丁目 E-mail: †{matusita,k\_ueno,asai,amemiya}@lalsie.ist.hokudai.ac.jp

**あらまし** LSI を間欠動作によって省電力化するためのタイマースイッチ回路を提案する。この回路はパルスを一定時間ごとに出力して後続の LSI を間欠動作させる。回路はリング発振器と負帰還ループからなり、リング発振のクロック信号を分周して間欠パルスを生成する。クロック信号の周期は基準の抵抗と容量で決める。クロック信号の分周方法によって間欠パルスの周期と幅を調節できる。回路内の MOSFET がすべてサブスレッショルド領域で動くように設計し、パルス生成の動作をシミュレーションで確認した。間欠パルスの周期と幅は数 $\mu$ s 一数日の範囲で任意に設定可能であり、消費電力は室温で  $0.2~\mu$ W であった。

キーワード CMOS, 間欠動作,参照クロック,発振器,極低消費電力

# Intermittent Pulse Generator for Ultra-Low Power LSIs

Hiromichi MATSUSHITA<sup>†</sup> Ken UENO<sup>†</sup> Tetsuya ASAI<sup>†</sup> and Yoshihito AMEMIYA<sup>†</sup>

† Faculty of Engineering, Hokkaido University

Kita 14, Nishi 9, Kita-ku, Sapporo, Hokkaido, 657-8501 Japan E-mail: † {matusita,k\_ueno,asai,amemiya}@lalsie.ist.hokudai.ac.jp

Abstract We proposed a timer circuit for the intermittent operation of ultra-lowpower LSIs. The circuit consists of a clock oscillator, an array of T-flip-flops, and a logic circuit to produce intermittent pulses. The clock oscillator is a ring oscillator controlled by a reference resistor and a capacitor, and generates stable clocks whose frequency is determined by the time constant of the reference resistor and capacitor. The T-flip-flop array accepts the clocks and produces divided pulses. The logic circuit accepts the clocks and divided pulses and produces an intermittent pulse to switch the power of LSIs. Theoretical analyses and SPICE simulation with 0.35-um CMOS parameters showed that the power dissipation of our timer circuit was 0.2 uW or less and that the period and width of the intermittent pulse could be controlled in a range from microseconds to days. Our timer circuit would be an useful device for the low-power operation of power-aware LSIs.

Keyword CMOS, intermittent operation, reference clock timer, oscillator, Ultra-low power

# 1. まえがき

近い将来には、多数のスマートセンサ LSI とそれらを結ぶネットワークからなるユビキタス情報環境の進展が予想される。このようなセンサネットワーク環境の実現に向けて、限られた電力消費のもとで各種の機能センシングを行うスマートセンサ LSI の開発が必要とされる[1,2]。これらセンサ LSI は極めて小さい消費電力での長期間動作が求められる。たとえば小型電池で数年にわたる動作が必要であり、さらには周囲環境(光、環境電磁界、温度差、振動など)からのエネルギー採取[3]による半永久動作が望まれている。したがってセンサ LSI の消費電力を低減することが不可欠である。

センサ LSI を低電力化するためには回路自体の電力削減も重要であるが、もう一つの有効な方法として、タイマースイッチによる LSI の間欠動作が挙げられる。たとえばデューティ比 1 %の間欠動作により消費電力を 1/100 に低減できる。間欠動作でも支障がない用途は多い[2]。ただしタイマースイッチそのものは連続動作なので本質的に低電力性を必要とする。

本研究では、LSI 間欠動作のための低電力タイマースイッチ回路を提案する[4]。消費電力を抑えるためクロック発振には簡単なリングオシレータを使用し、負帰還をかけて周波数を安定化する。その発振出力を分周して間欠動作のスイッチ信号を生成する。回路内のMOSFET をすべてサブスレッショルド動作[5]させる

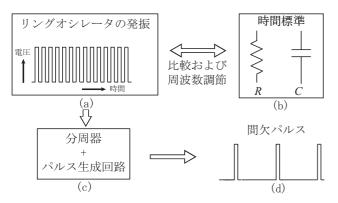

図1 タイマースイッチ回路の動作概念

ことで消費電力を抑える。この回路を設計してその動作を SPICE シミュレーションにより確認した。回路全体の消費電力は  $0.2\mu W$  以下を実現した。以下に回路動作の詳細を説明する。

# 2. 動作の概要

設計したタイマースイッチの動作概要を図1に示す。リングオシレータを発振させてクロック波形をつくる(図1(a))。時間基準となる抵抗RとキャパシタCを用意し(図1(b))、その時定数Eクロック波形の周期が等しくなるようにリングオシレータに負帰還をかけて周波数を安定化させる。このクロックを分周し(図1(c))、パルス生成回路で間欠周期あたり1パルスを抜き出して出力とする(図1(d))。この間欠パルスで主回路(LSI本体)の電源をスイッチして間欠的に動作させる。

タイマースイッチで重要なことは、間欠パルスの周期と幅を任意かつ正確に設定できることである。そのためには、リングオシレータの発振周波数をきちんと設定する必要がある。正確な周波数を発生するためには、水晶振動子や MEMS フィルタを用いることが一般的である。しかしここでは、製造コストと消費電力を共に抑えるため、簡単に抵抗と容量で発振周波数を決めることを考えた。次にその方法を説明する。

### 3. リングオシレータの周波数制御

#### 3.1 周波数を設定する方法

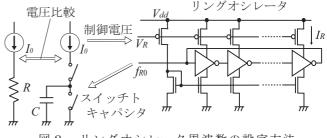

リングオシレータの周波数を設定する方法を<u>図2</u>に示す。まずリングオシレータの各インバータには電流制御用の MOSFET を付け、そのゲート電圧  $V_R$  によってリング発振周波数を制御する ( $V_R$ を下げる→電流  $I_R$  が増加→周波数が上昇)。次に、基準抵抗 R と基準容量 C を用意し、その容量 C をスイッチトキャパシタ回路で充放電する。これをリング発振出力(周波数  $f_{RO}$ )で駆動すれば、等価抵抗  $R_S$  は

図2 リングオシレータ周波数の設定方法

図3 周波数を設定する回路

$$Rs = 1/(f_{RO}C) \tag{1}$$

となる。いま電流制限 MOSFET のゲート電圧  $V_R$  を調節し、Rs = R となるようにリング発振周波数を設定したとする。このときの発振周波数は

$$f_{RO} = 1/(RC) \tag{2}$$

となり、基準のRとCの値で決められる値をとる。なおスイッチトキャパシタ抵抗とRの比較は、それぞれに同じ値の電流 $I_0$ を流して電圧を比較すればよい。

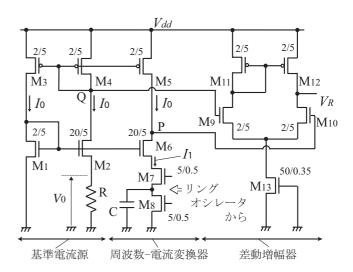

### 3.2 周波数を設定する回路の構成

以上の動作を行う回路を図3に示す。この回路は (i)基準電流源(M1-M5 と R), (ii)スイッチトキャパシタの周波数-電流変換器(M6-M8 と C), および (iii) 差動増幅器(M9-M13)からなる。差動増幅器の出力  $V_R$  でリングオシレータの電流制御 MOSFET のゲートを駆動する。そのリングオシレータの発振出力でスイッチトキャパシタの MOSFET スイッチ M7 と M8 を駆動する。なお、回路の MOSFET はすべてサブスレッショルド領域で動作させる(ただし M7 と M8 は強反転動作)。回路の各部分は次のように動作する。

# (i) 基準電流源

M2 のアスペクト比 (W/L) を M1 より大きく K 倍に とる。回路はサブスレッショルド動作なので、抵抗両端の電圧  $V_0$  は

$$V_0 = mkT \ln(K)/q \tag{3}$$

となる (m はサブスレッショルドスロープ係数, 約 1.5)。 したがって電流  $I_0$  は

$$I_0 = mkT \ln(K)/qR \tag{4}$$

である。この電流が MOSFET のサブスレッショルド領域 ( $I_0$  < 数百 nA) となるように抵抗 R の値を設定する。電流  $I_0$  は電流ミラーM5 によって周波数-電流変換器に入力される。

#### (ii) 周波数-電流変換器

M6 のアスペクト比を M2 と同じにとる。M7 と M8 をリング発振出力 (周波数 fRo) でオンオフ動作させると、スイッチトキャパシタ等価抵抗 Rs は 1/(fRoC)となり電流  $I_1$  が流れる。このとき Rs>R なら  $I_1<I_0$  でノード P の電位が上昇し、Rs<R なら  $I_1>I_0$  でノード P の電位が下降する。Rs=R のときはノード P と Q の電位がほぼ等しくなる。言い換えると

$f_{RO} < 1/(RC) \rightarrow P$  の電位は上昇  $f_{RO} > 1/(RC) \rightarrow P$  の電位は下降  $f_{RO} = 1/(RC) \rightarrow P$  の電位 = Q の電位となる。

#### (iii) 差動增幅器

ノードPとQの電位の比較結果をVRとして出力し、リングオシレータの電流制御 MOSFET を駆動する。発振出力 (周波数 fRo) がスイッチトキャパシタに帰還されているので

$f_{RO} < 1/(RC)$  のとき $\rightarrow$  P の電位上昇  $\rightarrow$   $V_R$ 低下  $\rightarrow$  リングオシレータの電流増加  $\rightarrow$   $f_{RO}$ 上昇

$f_{RO} > 1/(RC)$  のとき $\rightarrow$  P の電位低下  $\rightarrow$   $V_R$ 上昇  $\rightarrow$  リングオシレータの電流現象  $\rightarrow$   $f_{RO}$ 低下

という動作を生じて、最終的に  $f_{RO} = 1/1/(RC)$  の状態に落ち着く。なお差動増幅器のテール電流として M13 のオフ電流を使う。

図4 スイッチトキャパシタ駆動信号の発生

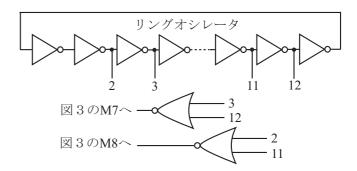

#### 3.3 スイッチトキャパシタの駆動パルス

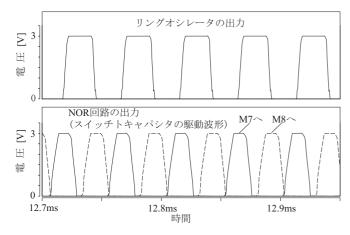

リングオシレータ出力でスイッチトキャパシタを駆動するとき、二つのスイッチ M7 と M8 が同時にオンとなってはならない。したがって M7 と M8 の駆動パルスは高レベルの期間が重ならないように設定する。そのため、ここでは図4に示すようにリングオシレータ内の適切な四つのノードから発振出力を取り出し、それらを二つの NOR ゲートに加えてオーバラップオシレータがインバータ 13 段から成るときは、3 段目と12 段目の出力を第一の NOR ゲートに加える。これによって重なりのない二つのパルスが得られる(後の図7を参照)。

# 4. 間欠パルスの生成

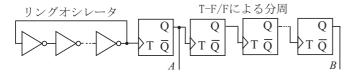

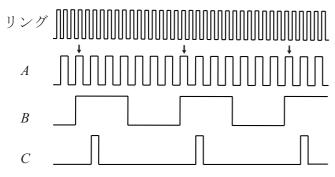

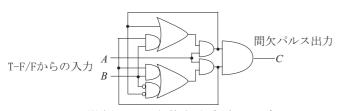

タイマースイッチ出力の間欠パルスを生成するため、 リングオシレータの発振出力を分周器と論理回路で加 工する。その概要を図<u>5</u>に示す。

はじめに図 5 (a)のようにリング発振出力を多段の T-F/F で分周する。最終段の T-F/F の出力(図 5 (b)の B) の周期が間欠パルスの周期となる。 次に、途中段の T-F/F から取り出す信号(図 5 (b)の A)によって間欠パルスの幅を決める。図は 1 段目の T-F/F から取り出した例である。出力 B が高レベルとなる期間内に出力 A のパルスを 1 個だけ抜き出し、それを間欠パルス(図 5 (b)の C) として出力する。分周の段数と A 信号の取り出し位置を選ぶことで、間欠パルスの周期と幅を広範囲に調節できる。

間欠パルスを抜き出すときには注意が必要である。 出力 A のパルス立ち上りに対して、出力 B は必ず遅れて立ち上がる。そのため、B の立ち上りを待ってから、すでに立ち上がっている A パルス(図の $\downarrow$ 印)を抜き出すと、間欠パルスの幅は A パルスの幅より狭くなってしまう。これを避けるためには、B が立ち上がった後で立ち上がる最初の A パルスを抜き出せばよい。その

(a) リング発振出力の分周

(b) T-F/F の出力波形

リング発振出力 および A:途中段 T-F/F の出力,

B: 最終段 T-F/F の出力, C: 間欠パルス出力

(c) 間欠パルスを抜き出す論理回路

図 5 間欠パルスの生成

ための論理回路を図5(c)に示す。

以上の回路すべてのインバータと論理ゲートには電流制限 MOSFET を付け、それによって消費電力を下げる構成とした。したがって間欠パルス生成回路もサブスレッショルド動作である。

# 5. 回路動作のシミュレーション

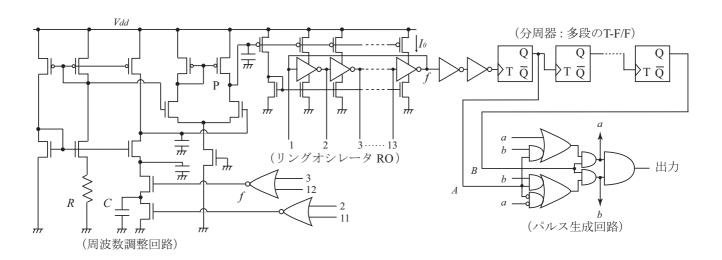

#### 5.1 回路の設計

以上の3要素(リングオシレータ、周波数設定回路、間欠パルス生成回路)を組み合わせて図6のような全体回路を設計し、SPICEシミュレーション上で動作を確認した。シミュレーション条件は次のとおりである:

- (i) 0.35 μm CMOS デバイスモデルを使用

- (ii) MOSFET のアスペクト値 (W/L) はμm 単位で

- ・リングオシレータは 1/0.35

- ・周波数設定回路は図3に記入のとおり

- ・間欠パルス生成回路も 1/0.35

- (ii) 電源電圧 = 3 V (リチウム電池を想定)

- (iii) スイッチトキャパシタの容量 C=5 pF

- (iv) リングオシレータのインバータ段数 = 13

- (v) 間欠パルス生成回路の各インバータと各論理ゲートの最大電流を 10 nA に制限。

周波数設定回路の基準抵抗 R は 10 M  $\Omega$  を中心に変化させた。 R=10 M  $\Omega$  のとき図 3 の電流  $I_0$  は 10 nA であった。この基準抵抗をチップ上に搭載することは可能である(高抵抗用ポリシリコン  $1k\Omega/\square$  を使って 300  $\mu$  m 角)。しかし外付け抵抗として間欠パルスの周期を変えられるようにしても良い。

図6 全体の回路構成

図7 スイッチトキャパシタ駆動パルスの波形

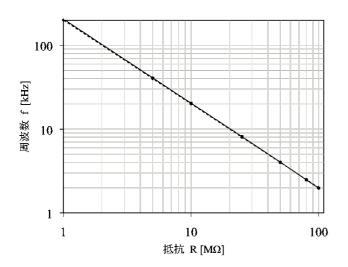

図8 抵抗値による発振周波数の制御(点線は理論値)

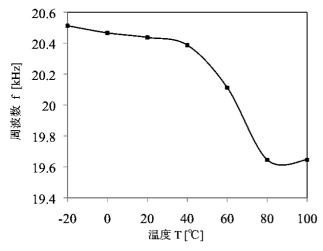

図9 発振周波数の温度変化

# 5.2 リングオシレータの動作

基準抵抗 R=10 M $\Omega$  のとき予想される発振周波数は 1/(RC)=20 kHz である。そのときのリングオシレータ

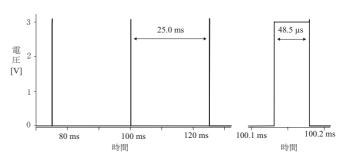

図10 間欠パルスの出力例 左:パルス発生の様子 右:間欠パルスの時間拡大

発振波形とスイッチトキャパシタ駆動波形を図7に示す。発振周波数は 20.4 kHz であった。

次に R の値を 1 M $\Omega$  から 100 M $\Omega$  まで変えたときの発振周波数を  $\underline{08}$  に示す。周波数は 2 kHz から 200 kHz までの広範囲に変化し、1/(RC)で予想される値(点線) からの誤差は平均 2 %であった。

発振周波数は温度によって多少変化する。 図9には R=10 M $\Omega$ 一定として温度を変化させたときの発振周波数を示す。抵抗 R は温度変化なしと仮定した。発振周波数は負の温度係数をもつ。なお、高抵抗用ポリシリコンは負の温度係数を持つので、それを抵抗に使えば発振周波数の温度依存性を一部打ち消すことができる。

# 5.3 間欠パルスの出力

間欠パルスの周期と幅は、間欠パルス生成回路の分周段数(T-F/F の個数)とA信号取り出し位置によって決まる。シミュレーションでは、パルス幅は数 $\mu$ s 〜数日の範囲(周期は幅より長い時間)に設定可能であった。一例として、R=10 M $\Omega$  で分周が9段、かつA信号を1段目のT-F/F から取り出したときの間欠パルス出力を図10に示す。パルス幅は48.5  $\mu$ s、間欠周期は25 ms であり、その比は予想値の1:512とほぼ同じであった。

なお、図 5 (a)のように単純な T-F/F 列で分周すると、パルス幅と周期はそれぞれ 2 倍ごとの調節幅になる。細かく調節したい時には、T-F/F 列に論理回路を加えてパルス計数回路を作ればよい。

分周段数を増やせば間欠パルスの幅と周期はいくらでも長くできる。しかしリングオシレータ周波数の設定誤差が2%くらいあるので、あまり長い周期に設定すると間欠パルス発生のタイミングが正しく予測できなくなる(たとえば正午にパルス発生の予定が夕刻にずれるなど)。したがって、実用的な観点からみれば、周期は1時間以下、パルス幅はその1/100~1/10000程度が使い易い条件と思われる。

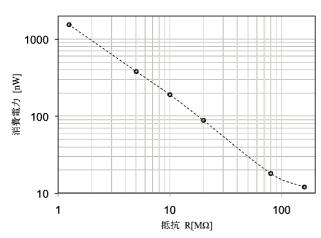

図 11 消費電力と抵抗 R の関係。間欠パルス生成回路の構成を R の値ごとに調整して、間欠パルスの周期を 2048 ms、幅を 4 ms と一定に設定。

# 5.4 消費電力

# 6. まとめ

LSI システムを極低電力動作させるためのタイマースイッチ回路、すなわち間欠パルス回路を提案した。この回路は周波数を制御したリングオシレータの出力を分周加工して間欠パルスを生成する。周波数制御は基準抵抗と容量で行う。回路を設計し、SPICE シミュレーションにより、その動作を確認した。間欠パルスの周期と幅は数 $\mu$ s 一数日の範囲で任意に設定できる。消費電力は  $0.2~\mu$ W 以下に抑えることが可能であった。この回路は微小電力の動作が要求される待ち受け型レシーバ(wake-up receiver)[6,7]やセンサーネットワークのノード LSI 等への適用に適している。

# 文 献

- [1] A.P.Chandrakasan, D.C.Daly, J.Kwong, and Y.K.Rama dass, "Next generation micro-power systems," in *Proc. IEEE Symp. VLSI Circuits*, 2008, pp. 2-5.

- [2] K. Ueno, T. Hirose, T. Asai, and Y. Amemiya, "CMOS smart sensor for monitoring the quality of perishables," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 798–803, Apr. 2007.

- [3] P. Fiorini, I. Doms, C. Van Hoof, and R. Vullers, "Micropower energy scavenging," in *Proc. 34th European Solid-State Circuits Conf. (ESS- CIRC)*, 2008, pp. 4-9.

- [4] 松下 拓道, 上野 憲一, 浅井 哲也, 雨宮 好仁, "サブスレッショルド CMOS 回路による間欠動作スイッチ,"電子情報通信学会ソサイエティ大会, (新潟), 2009.

- [5] A. Wang, B. H. Clhoun, and A. P. Chandracasan, Sub-Threshold Design for Ultra Low-Power Systems. New York: Springer, 2006.

- [6] N. Pletcher, J. Rabaey, S. Gambini. "A 52 μW Wake-Up Receiver With -72 dBm Sensitivity Using an Uncertain-IF Architecture". *IEEE Journal of Solid* State Circuits, vol. 44, no.1, pp.269-280, Jan. 2009.

- [7] T. Umeda, H. Yoshida, S. Sekine, Y. Fujita, T. Suzuki, and S. Otaka, "A 950-MHz rectifier circuit for sensor network tags with 10-m distance," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 35-41, Jan. 2006.