# サブスレッショルド領域で動作するアナログ CMOS 回路によるカオス発生器

A Chaotic Oscillator using Subthreshold Analog CMOS Circuits

神谷 泰史 金澤 雄亮 浅井 哲也 雨宮 好仁 Kamiya Taishi Kanazawa Yusuke Asai Tetsuya Amemiya Yoshihito

### 北海道大学 工学部

Department of Electrical Engineering, Hokkaido University

## 1 はじめに

自然界で一般に観測されるカオスは、空間的な自由度を持ち、時間 / 空間的に乱れた振る舞いを引き起こす「時空カオス」である。構成論的なアプローチを用いて、この時空カオスの理解、新現象の予言をしようとする研究が行なわれている。Coupled Map Lattice(CML), Global Coupled Map(GCM)[1] はその代表的な例である。本稿では構成論的なアプローチを用いて、VLSI上にカオス系を構成する。現在の VLSI 技術を用いれば、時空カオス系の単位要素であるアナログのカオス発生回路を多数集積可能になる。アナログ電子回路を用いることで、より自然に近い、連続時間、かつ各要素の状態が連続である系を構成できる。本稿ではその第一段階として、VLSI 上に多数実装可能なカオス発生回路を提案する。提案する回路は Lotka-Volterra モデルに基づくカオス発生回路である。

2 Lotka-Volterra モデルに基づくカオス発生回路2 被食者-1 捕食者 Lotka-Volterra 系の方程式は、

$$\begin{cases}

\tau \dot{x_1} = (1 - x_1 - x_2 - ky)x_1 \\

\tau \dot{x_2} = (a - bx_1 - cx_2 - y)x_2 \\

\tau \dot{y} = (-r + \alpha kx_1 + \beta x_2)y

\end{cases} \tag{1}$$

のように表される。au は時定数である。ここで、パラメータ $a,b,c,k,r,\alpha,\beta$  を適切な値に設定することで、変数  $x_1,x_2,y$  のアトラクタがカオスを呈する [2]。式 (1) は変数の乗算を含んでいるため、電子回路化する際に乗算器を必要とし回路規模が大きくなる。そこで、 $X_1=\ln x_1,X_2=\ln x_2,Y=\ln y$  なる変数変換を行う。変数変換により、式 (1) は

$$\begin{cases}

\tau \dot{X}_{1} = 1 - \exp(X_{1}) - \exp(X_{2}) - k \exp(Y) \\

\tau \dot{X}_{2} = a - b \exp(X_{1}) - c \exp(X_{2}) - \exp(Y) \\

\tau \dot{Y} = -r + \alpha k \exp(X_{1}) + \beta \exp(X_{2})

\end{cases} (2)$$

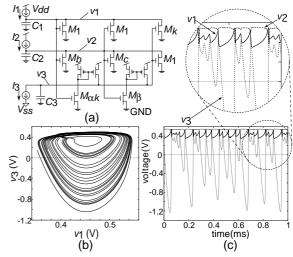

となる。式 (2) 中の指数関数項は、MOSFET のサブスレッショルド領域での飽和 I-V 特性  $[I_{ds} \sim I_0 \exp{(V_{gs}/v_0)},$  ここで  $V_{gs}$  はゲート-ソース間の電位差、 $v_0$  は規格化パラメータ] より、トランジスターつで表すことができる。したがってカオス発生回路を簡単な回路で構成可能である。提案するカオス発生回路の回路構成を図 1(a) に示す。電流  $I_1,I_2,I_3$  を  $I_1:I_1:I_3=1:a:r$  と設定する。また、MOSFET のゼロバイアス電流  $I_0$  (  $\sim W/L$  ) の比が  $M_1:M_b:M_c:M_k:M_{\alpha k}:M_{\beta}=1:b:c:k:\alpha k:\beta$  となるようにトランジスタのサイズを決定する。

図 1 (a) カオス発生回路,  $(b)v_1$ - $v_3$  平面でのアトラクタ, (c) 変数の時間変化

# 3 シミュレーション結果

回路シミュレーションにより、図 1(a) の回路の動作を確認した。カオスを発生させるためのパラメータを、文献 [2] をもとに決定した。電流源の電流値を  $I_1=100$  nA,  $I_2=99.2$  nA,  $I_3=90$  nA と設定した。MOSFET のチャネル長 L=1.6  $\mu m$  とし、ゲート幅 W を  $W_{M_1}=6.4$   $\mu m$ ,  $W_{M_b}=9.6$   $\mu m$ ,  $W_{M_c}=6.4$   $\mu m$ ,  $W_{M_b}=9.6$   $\mu m$  とした。また、 $C_1$ ,  $C_2$ ,  $C_3=1$  pF とした。シミュレーション結果を図 1(b), 1(c)0 に示す(1(c)1 の相平面でのアトラクタ [図 1(c)1]、1(c)2 の時間変化 [図 1(c)3 の結果より、1(c)3 の軌道がストレンジアトラクタを呈することを確認した [図 1(c)3]。このアトラクタがカオスであることを確認した [図 1(c)3]。このアトラクタがカオスであることを確かめるために、リャプノフ指数(1(c)4 の結果、最大リャプノフ指数は 1(c)5 を計算した。その結果、最大リャプノフ指数は 1(c)6 であった。このことは、構成した回路がカオスを発生することを示す。

Lotka-Volterra モデルに基づくカオス発生回路を提案し、回路がカオスを発生することを確認した。提案した回路はトランジスタ数が少なく、CMOS と容量の小さいキャパシタのみで構成できるため VLSI 上へ多数実装可能である。

#### 参考文献

- [1] 金子 邦彦, 津田 一郎, 複雑系のカオス的シナリオ, 朝倉書店, 東京、1996.

- [2] 森田 善久, カオス全書 3 生物モデルのカオス, 朝倉書店, 東京,