# 抵抗変化型メモリをシナプスに用いた ニューラルネットワークにおける教師有り学習回路

A Memristor-CMOS-Hybrid Neural-Network for Simple Supervised Learning

赤穂伸雄 Nobuo Ako 浅井哲也 Tetsuva Asai 雨宮好仁 Yoshihito Amemiya

北海道大学 大学院情報科学研究科

Graduate School of Information Science and Technology, Hokkaido University

#### 1 まえがき

近年、不揮発性メモリの大容量化を目指した抵抗変化型メモリ (ReRAM) の研究が盛んに行われている [1]。この素子は電気的には抵抗素子であるが、その抵抗値の書き換え (記憶) が可能である。そこでシナプスに ReRAMを利用したニューラルネットワークハードウエアに関する研究が行われている [2]。今回我々はシナプスに ReRAMを用いた学習機能を持つニューラルネットワーク(単純パーセプトロン)電子回路を構成し、素子レベルで回路シミュレーションを行った。

## 2 ReRAM

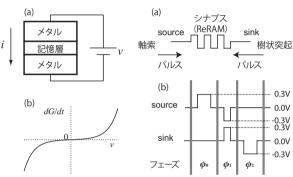

ReRAM の概略図を図 1a に示す。この素子は金属酸化膜や有機物の記憶層を金属で挟んだ構造を持つ 2 端子素子である。ここではバイポーラ型の ReRAM (memristor)を用いる。バイポーラ ReRAM の電流(i)は i=Gv(vは ReRAM の両端間の電圧)で与えられる。ここで、Gは素子の可変コンダクタンスである [2]。G の時間変化は  $dG/dt=KG\sinh(Mv)$  で与えられる(K,M は定数)。dG/dtと電圧 v の関係を図 1b に示す。

## 3 ReRAM をシナプスとして用いるための基本方針

今回我々は、Snider が提案した方針 [2] をもとにニューラルネットワークの回路を構成した。シナプスの軸索側を source、樹状突起側を sink と呼ぶ。sink の電圧が source より高い時に G が増える(図 2a)。回路は離散時間で動作し、1 回の動作は三つのフェーズに分かれる(図 2b)。軸索側のニューロンが発火したときは、 $\phi_0$  で正の電圧パルスが立ち、 $\phi_1$  で負のパルスが立つように source の電圧が制御される。樹状突起側のニューロンが発火したときは、 $\phi_1$  で正のパルスが立ち、 $\phi_2$  で負のパルスが立つように sink の電圧が制御される。ここでパルスの振幅は全て同じであり、 $\phi_0,\phi_2$  のパルス幅を $\phi_1$  に比べ長くする。 source と sink の片方のみが発火したときは、 $\phi_1$  のパルス幅が  $\phi_0,\phi_2$  と比べ短いため G は減少する。 source と sink の両方が発火したときは、 $\phi_1$  でパルス振幅の倍の電圧が素子にかかるため図 1b の非線形性により G が大きく増加し、G は増加する。

### 4 回路アーキテクチャとシミュレーション

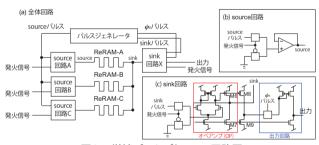

前節の ReRAM シナプスを用いて単純パーセプトロンを構成した(図 3a)。前節で説明した "source パルス"、 "sink パルス" および、フェーズ  $\phi_0$  でパルスが立つ時に 論理 1(それ以外では 0)を出力する " $\phi_0$  パルス"を出力する回路を設計した(パルスジェネレータ)。この回路はカウンタと論理回路で構成した。前節で説明したように source の電圧を制御するため、マルチプレクサとボルテージフォロアを持つ source 回路を構成した(図 3b)。同様に sink の電圧を制御するため、マルチプレクサとボルテージフォロアを持つ sink 回路を構成した(図 3c)。また sink 回路の出力を得るため、オペアンプ (OP) から ReRAM へ流れるの電流を出力回路にコピー (M8,M9 のゲート電圧を M6,M7 と同じにする事で同じ電流を流す)し、出力回路ではコピーされた電流を  $\phi_0$  で取り出して二値化するよう構成した(図 3c)。

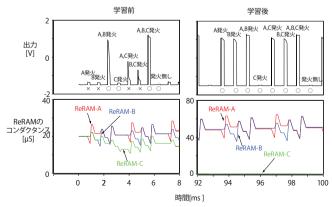

提案回路の SPICE シミュレーションを行った。シミュレーションを行うにあたり、ReRAM モデルの等価回路を作った。今回のシミュレーションでは、source 回路を三つ(A,B,C)、sink 回路を一つ(X)用意(図 3a)し、A または B が発火した時、X を発火させた。SPICE シミュレーションの結果を図 4 に示す。学習前は誤った出力を出しているが、学習後は所望の結果がえられた。この結果は、ReRAM(memristor)と CMOS を組み合わせたハイブリッドニューラルネットワークが単純な回路で実装できる事を示している。

図1 ReRAMとコンダクタンス特性 図2 ReRAMの配置と発火パルス

図3 単純パーセプトロンの回路図

図4 SPICEシミュレーション結果

#### 参考文献

$[1] A. \ Sawa, \ Materials \ Today, \ 11(6), \ 28, \ 2008.$

[2]G. S. Snider, Nanotechnology 18, 1, 2007.