## サブスレッショルド SRAM セルの検討 ~ 完全サブスレッショルド型とテイル電流制限型の比較 ~

Investigation of Subthreshold SRAM Design for Low Power Operation

吉田 和徳

宇田川 玲

浅井 哲也

雨宮 好仁

Kazunori Yoshida

Akira Utagawa

Tetsuva Asai

Yoshihito Amemiya

北海道大学 大学院 情報科学研究科

Graduate School of Information Science and Technology, Hokkaido University

## 1 まえがき

サブスレッショルド SRAM セルの実現に向けて 2 の方法を検討した。1 つ目は「完全サブスレッショルド型ラッチと多数決論理回路を組み合せた SRAM セル」である。SRAM の消費電力は  $V_{dd}^2$  に比例するため、 $V_{dd}$  を  $V_{th}$  以下にすれば消費電力を大きく削減できるが、セルの不良率増大が問題である。複数のラッチ回路を一つのセルとみなし多数決論理を行なえば低消費電力化と不良率低減の双方を実現できるかもしれない。2 つ目の手法として「テイル電流制限型メモリセル」を提案する。回路中を流れる電流をトランジスタのリーク電流と同等に抑える事によって低消費電力動作を実現する。

## 2 多数決論理を行なう低電圧 SRAM メモリセル

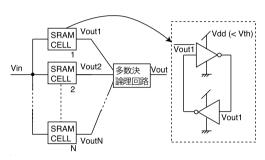

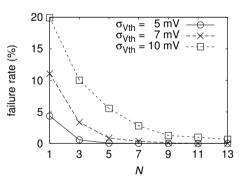

図1に提案手法を示す。1つのSRAMセルはN個の ラッチ回路で構成され、出力  $V_{out}$  は N 個のラッチ回路 の出力の多数決をとり多数になったものとする。Nと不 良率の関係を求めるため HSPICE によるモンテカルロ シミュレーションを行なった。ただし、 $0.35~\mu m$  CMOS プロセスパラメータを使用し、 $V_{dd} = 0.40 \text{ V}$  とし、トラ ンジスタの絶対零度しきい値のバラツキ (ガウス分布を 想定:  $\sigma_{Vth} = 5 \text{ mV}, 7 \text{ mV}, 10 \text{ mV}$ ) を考慮した。図 2 に その結果を示す。Nの増加に従って不良率は0%に漸近 し、提案手法は不良率の低減に効果的であることが確認 できた。 $V_{dd} = 0.40 \text{ V}, \sigma_{Vth} = 10 \text{ mV}$  の時、約5%の不 良率を得るためには N=5 に設定する必要があり、そ の時の平均消費電力 (1 kHz 動作の時の待機および動作 時の平均) は940 fW であった。一方 N = 1(多数決論理 を行なわない場合)にて同等の不良率を実現するのに必 要な V<sub>dd</sub> は 0.41 V であり、その時の平均消費電力は 200 fW となる。よって多数決論理を行なう低電圧 SRAM セ ルは効果的ではないことがわかった。

## 3 テイル電流制限型メモリセル

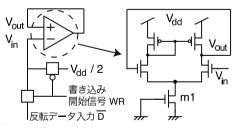

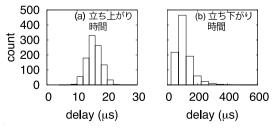

図 3 にテイル電流制限型メモリセルの回路構成を示す。 提案回路は 2 つの MOS スイッチとポジティブフィード バックを持つ OP アンプから構成されている。WR = '1' の時データ入力  $\bar{D}$  によってセルの内部電位  $V_{out}$  が 書き換わる。WR = '0' の時  $V_{in} = V_{dd}/2$  となり、現在 の  $V_{out}$  の値を保持する (待機状態)。m1 のゲート電位の 0 V にする事で OP アンプのテイル電流はリーク電流の オーダーになるため消費電力が最小となる。モンテカル ロシミュレーションを行ない  $V_{out}$  の書き換えの遅延時間 のヒストグラムを計算した。ただし  $0.35~\mu m$  CMOS プ ロセスパラメータを使用し $V_{dd}=3.3~\rm V$ とした。図 4(a)および (b) から遅延時間は最大で  $500\mu s$  程度であり、約  $1~\rm kHz$  での動作が可能である事がわかった。

図 1 完全サブスレッショルド型ラッチ+多数決論理回 路による SRAM メモリセル

図 2 素子数 N とセルの不良率の関係

図3 テイル電流制限型メモリセルの回路構成

図 4 遅延時間のヒストグラム