## 単電子回路による多数決論理デバイス

A Majority-Logic Device Using a Balanced Pair of Single-Electron Boxes

北海道大学 工学部\*/量子集積エレクトロニクス研究センター 大矢剛嗣\*浅井哲也\*福井孝志\*\*

Hokkaido University, Department of Electrical Engineering \* & RCIQE \*\* O oya Takahide\*, A sai Tetsuya\*, Fukui Takashi\*\*, Amemiya Yoshihito\*

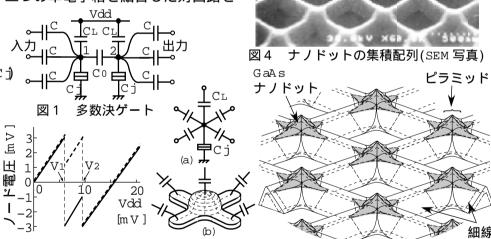

あらまし 単電子回路を用いた多数決論理デバイスを提案する。二つの単電子箱を結合した対回路を 多数決ゲートとして使用する。このゲートは入力信号によって 生じる不均衡を利用して多数決論理を出力する。ゲートデバイ スと応用回路の動作をシミュレーション上で示すとともに、選 多数決論理ゲート ゲートデバイスを図1に示す。単電子箱(CL-C) を二つ接続して対にする。この対回路のノード1とノード2の電 位を励起電圧Vddの関数として図2に示す。Vddが二つのしきい れかに電子がトンネルして安定する。それに対応して両ノード の電位が正と負に分かれる。ゲートの出力は、入力(論理1は正 電圧、論理0は負電圧)の多数決に応じた理論値をとる。 ゲートの製作方法 本ゲートは図3(a)の単位要素を二つ結合 したものである。単位要素をつくるためには、図3(b)のような 「四つの結合枝をもつ微小ドット(ナノドット)を形成すれば よい。そのためのプロセスとして、有機金属気相選択成長法 に基づく作成方法を開発中である。第一段階として、GaAs基 板上の絶縁膜の上にGaAsナノドットを配列する事に成功し ている(図4. 図5)。 \*K.Kuwam ura, J.M otohisa, and T.Fukui, J.Crystal Growth, 170, pp. 700-704 (1997).

対回路のノード電圧 (実線と点線)

単位要素 (ナノドット)

図5 ナノドット配列の拡大模式図 (灰色がGaAsナノドット;他はAIGaAs)