## 低電圧CMOSディジタル集積回路のためのPVTバラツキ補償技術

-Process, supply voltage, and temperature compensation circuit for low-voltage CMOS digital circuits-

次田 祐輔¹, 上野 憲一¹, 廣瀬 哲也², 浅井 哲也¹, 雨宮 好仁¹

1北海道大学大学院 情報科学研究科 情報エレクトロニクス専攻 2神戸大学 工学研究科 電気電子工学専攻

http://lalsie.ist.hokudai.ac.jp/jp/ tsugita@lalsie.ist.hokudai.ac.jp

## 背景

- 1.  $V_{nn}$ の低減 2. 高 $V_{th}$ トランジスタ

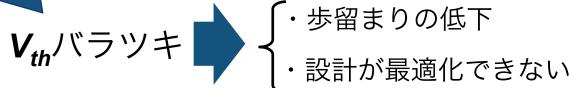

## ディジタル回路の動作速度バラツキの増大

# 背景一バラツキ

## "プロセス誤差"

## "温度変化"

#### 1.WIDバラツキ

(within-die)

→ 相対精度が変化

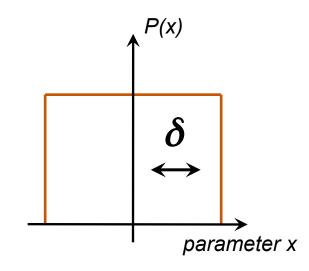

### 均一分布を想定

$\delta V_{th}$ ,  $\delta \mu$ ,  $\delta C_{ox}$ ,  $\delta L$ ,  $\delta W$ ,...

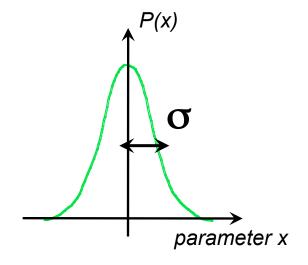

#### 2.D2Dバラツキ

(die-to-die)

→ 絶対値が変化

## ガウス分布を想定

$\sigma_{\mathsf{Vth}}$ ,  $\sigma_{\mu}$ ,  $\sigma_{\mathsf{Cox}}$ ,  $\sigma_{\mathsf{L}}$ ,  $\sigma_{\mathsf{W}}$ ,  $\cdots$

### 3.温度バラツキ

$$\longrightarrow V_{th}$$

と $\mu$ が変化

$$V_{th} \sim V_{th0} - \kappa (T_0 + \delta T)$$

$$\mu \sim \mu_0 \left( \frac{T_0 + \delta T}{T_0} \right)^{-m}$$

**V<sub>th0</sub>→**絶対零度(0K)での**V<sub>th</sub>**

*μ₀*→ 室温(300K)での*μ*

*m*→1.5

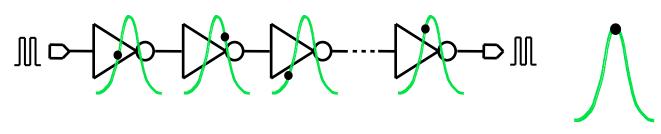

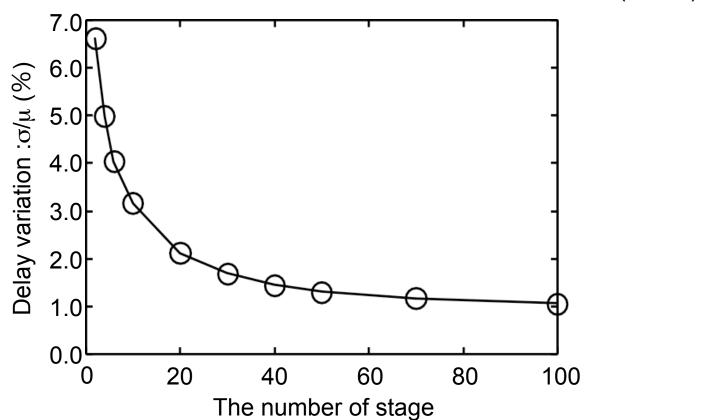

## 背景一1.WIDバラツキ

## "ランダム成分の平均化

#### 【インバータチェーン遅延時間バラツキの段数依存性】

ランダムバラツキのみを考慮したモンテカルロシミュレーション(100回)

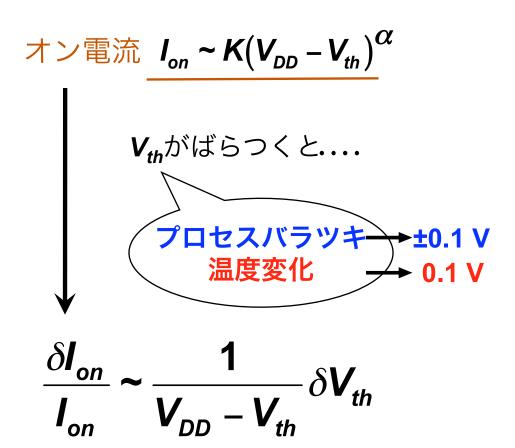

# 背景一2.D2Dバラツキ

動作速度:

$$\tau = \frac{C_{load}V_{DD}}{I_{on}}$$

動作速度:

$$\tau = \frac{C_{load}V_{DD}}{I_{on}}$$

$$I_{on} \sim \frac{W}{L} \mu C_{ox} (V_{DD} - V_{th})^{\alpha}$$

$$\rightarrow \text{トランジスタの飽和式}$$

$$C_{load} \sim C_{ox} LW$$

$$\rightarrow \text{次段のゲート容量}$$

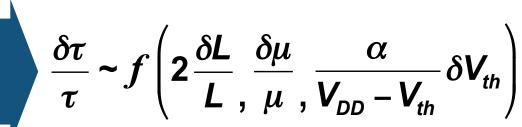

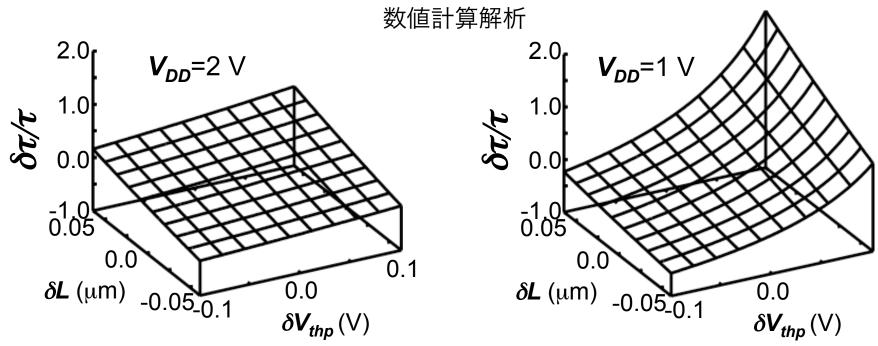

## 動作速度バラツキ

#### 【インバータチェーン遅延時間バラツキの電源電圧依存性】

低電圧ではV<sub>th</sub>バラツキにより動作速度バラツキが増大

## 背景一3.温度バラツキ

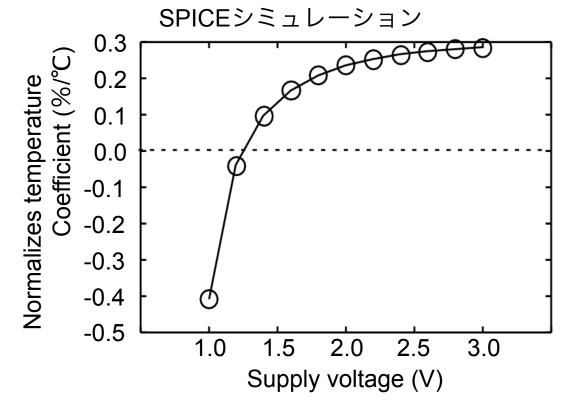

## 動作速度バラツキ

動作速度:

$$\tau = \frac{C_{load}V_{DD}}{I_{on}}$$

$$\frac{\delta \tau}{\tau} \sim \left[\frac{m}{T_0} - \frac{\alpha \kappa}{V_{DD} - V_{th0} + \kappa T_0}\right] \delta T$$

#### 【インバータチェーン遅延時間バラツキ温度係数の電源電圧依存性】

"<u>低電圧ではV<sub>th</sub>バラツキにより動作速度バラツキが増大</u>"

## 目的

低電圧CMOSディジタル回路の動作速度バラツキ補正

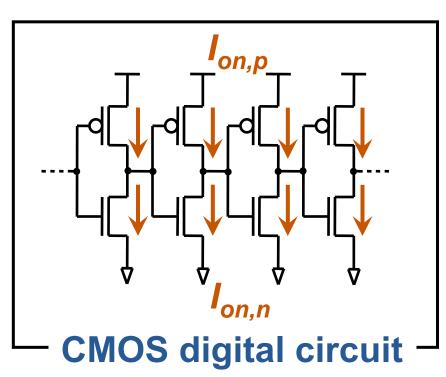

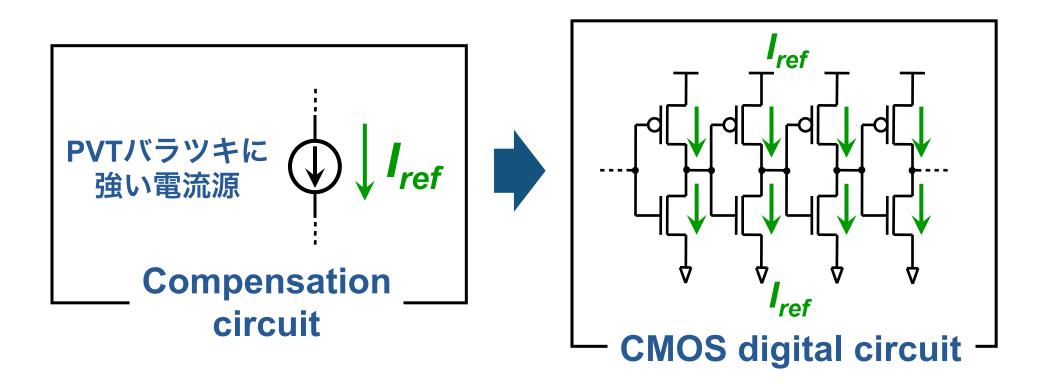

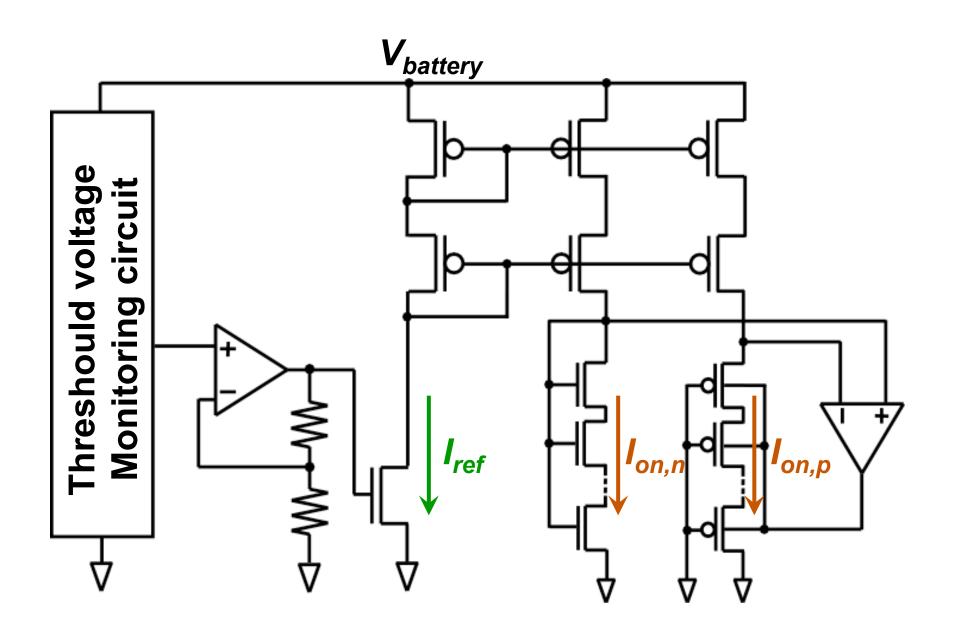

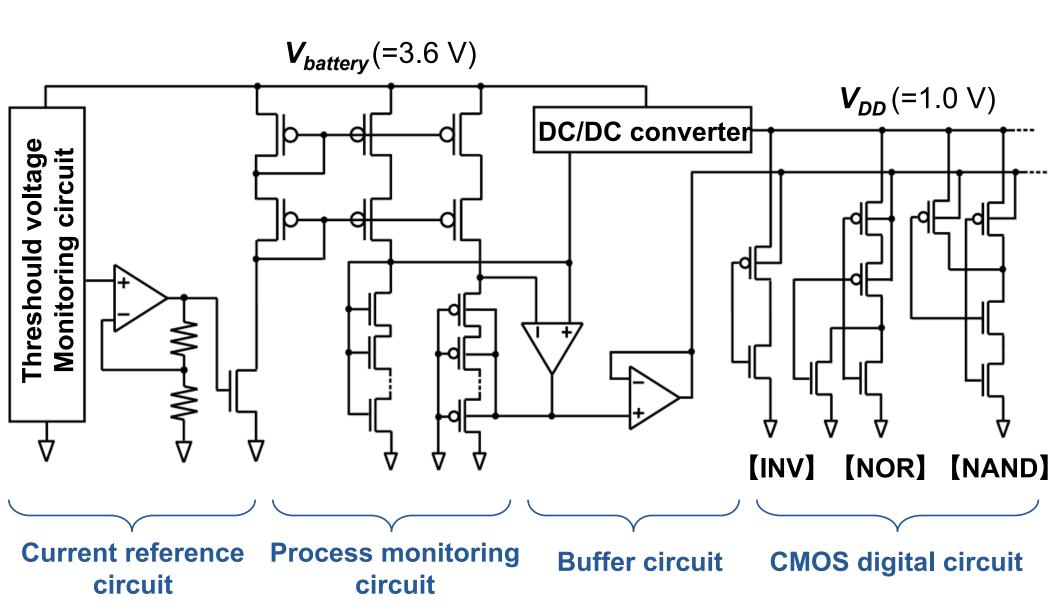

## バラツキ補正アーキテクチャ

ディジタル回路のオン電流バラツキの補正

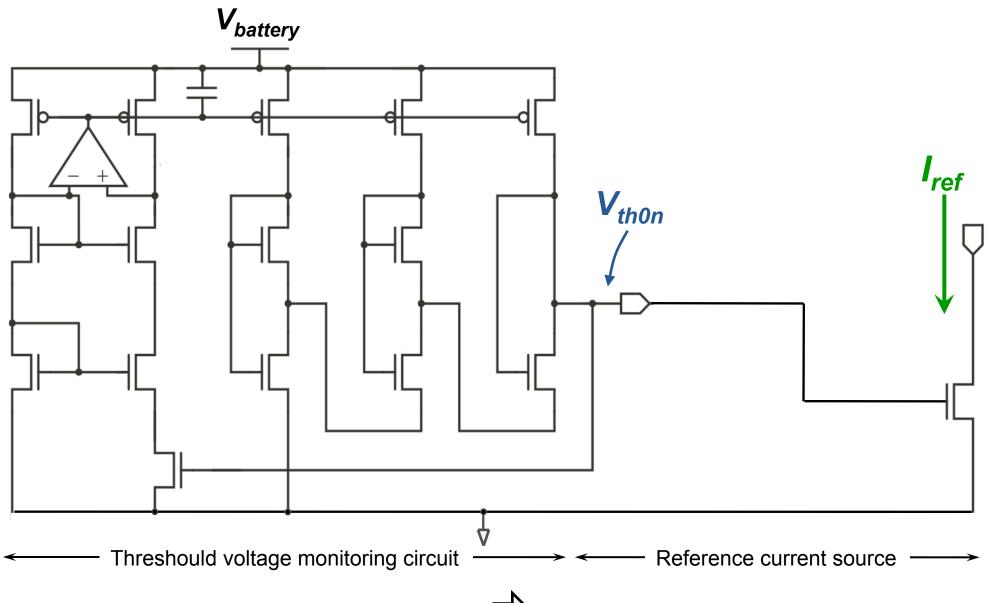

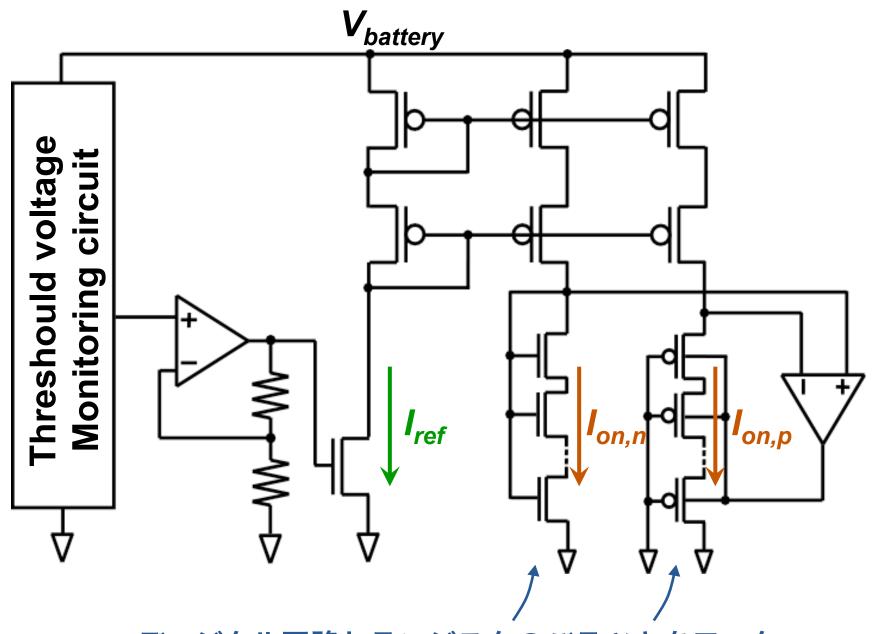

## 電流源(1)

$V_{thOn}$ : 絶対零度でのしきい値電圧  $\Box$  プロセスの $V_{th}$ バラツキをモニタ

Ueno K., Hirose T., Asai T., and Amemiya Y., "A 0.3-μW, 7 ppm/°C CMOS voltage reference circuit for on-chip process monitoring in analog circuits," ESSCIRC, pp. 398-401, (Sep. 15-19, 2008).

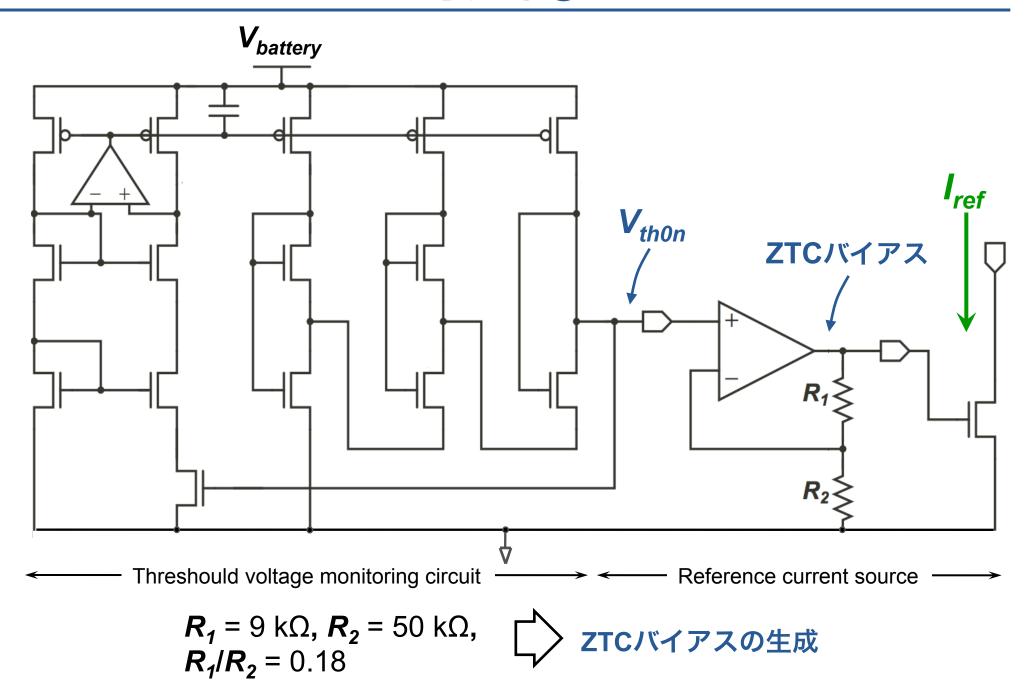

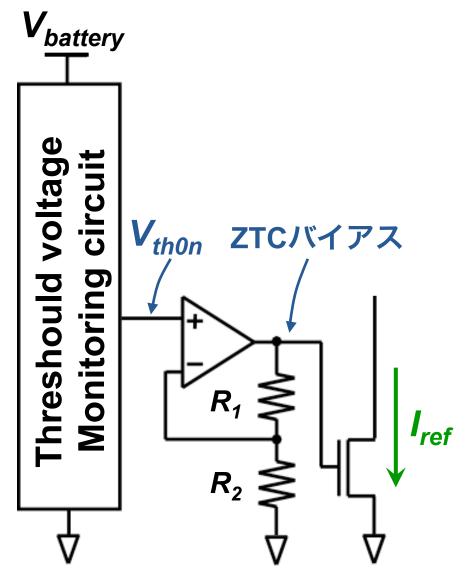

## 電流源②

Ueno K., Hirose T., Asai T., and Amemiya Y., "A 300 nW, 7 ppm/°C CMOS voltage reference circuit based on subthreshold MOSFETs," ASSCC, pp. 95-96, (Jan. 19-22, 2009).

# 電流源③

$$I_{ref} = K \left\{ V_{THO} \left( 1 + \frac{R_1}{R_2} \right) - V_{TH} \right\}^{\alpha}$$

Temp. Coefficient

$$TC_{I} = \frac{1}{I_{DS}} \frac{\partial I_{DS}}{\partial T} = -\frac{m}{T} + \frac{\alpha \kappa}{V_{TH0} \left(1 + \frac{R_{1}}{R_{2}}\right) - V_{TH}}$$

•  $R_1/R_2$  for TC=0

$$\frac{R_1}{R_2} = \left(\frac{\alpha}{m} - 1\right) \frac{\kappa T}{V_{TH0}}$$

# オン電流バラツキ補正回路①

ディジタル回路トランジスタのバラツキをモニタ

# オン電流バラツキ補正回路②

nMOSFET—→"電源電圧"

pMOSFET──"基板電位"

# オン電流バラツキ補正回路③

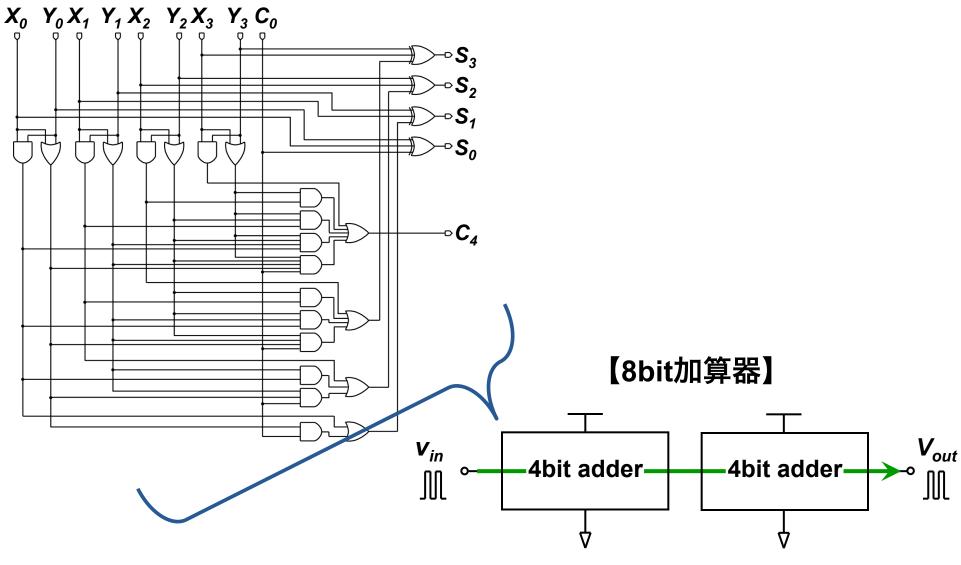

# 桁上げ先見型加算器

## 【4bit桁上げ先見加算器】

**Critical pass:** Delay

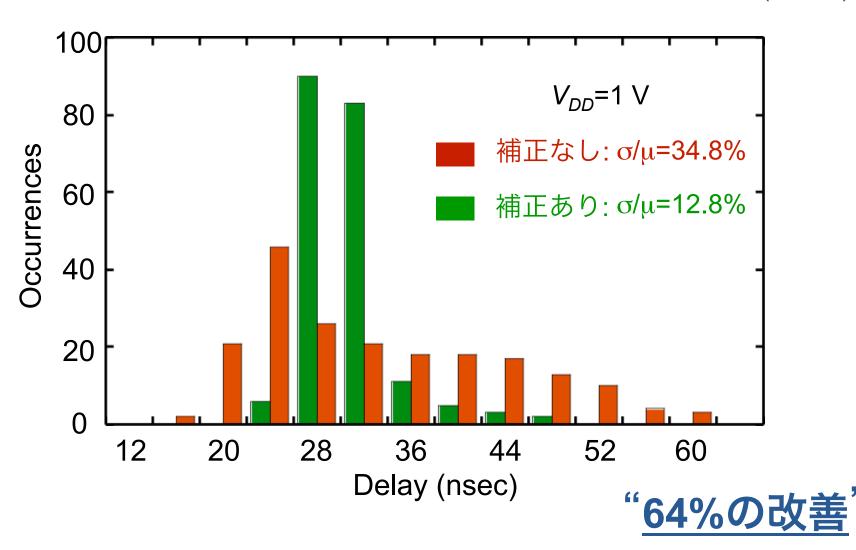

## シミュレーション結果

Process: 0.35 μm 2P-4M CMOS

8bit桁上げ先見加算器の遅延時間バラツキ

WID&D2Dバラツキを考慮したモンテカルロシミュレーション(200回)

# シミュレーション結果

Process :  $0.35 \mu m$  2P-4M CMOS

8bit桁上げ先見加算器の遅延時間バラツキ

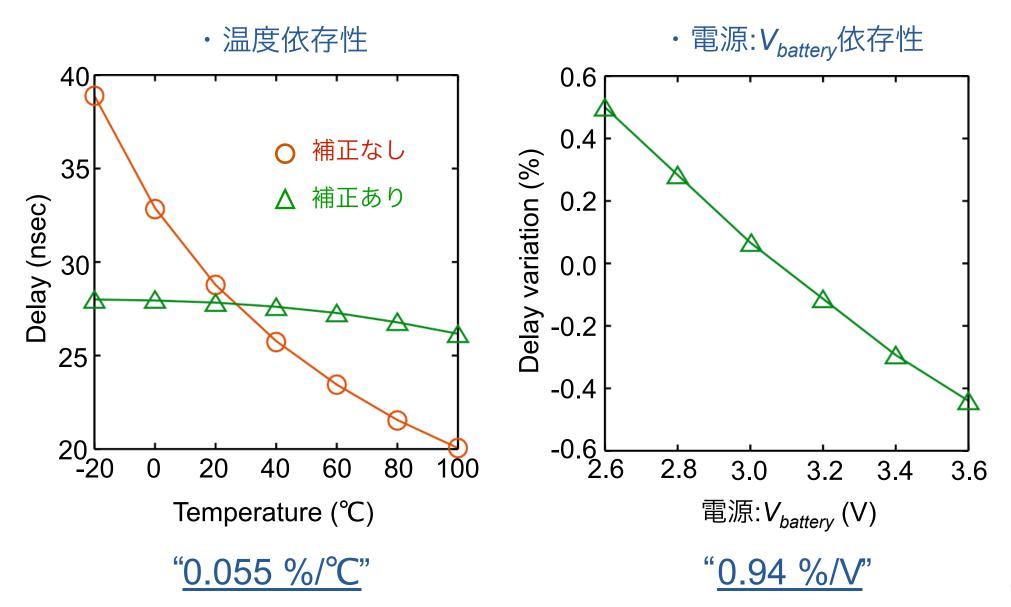

## まとめ

・定電流源を用いたバラツキ補正回路を提案

プロセスバラツキ → 64%改善

温度変化 → 0.055 %/℃

電源変動 → 0.94 %/V

今後……最先端プロセスへの応用