# Analog CMOS Implementation of a Bursting Oscillator with Depressing Synapse

# Kazuki Nakada, Tetsuya Asai, and Yoshihito Amemiya

Department of Electrical Engineering, Hokkaido University North 13, West 8, Sapporo, 060-8628, Japan nakada@sapien-ei.eng.hokudai.ac.jp www: http://sapiens-ei.eng.hokudai.ac.jp/

# Abstract

The present paper proposes an analog CMOS circuit that implements a bursting oscillator with a depressing synapse. Bursting oscillation arises the result of interaction between a fast excitatory subsystem and a slow subsystem. We employ an analog circuit, called the hardware Oregonator, for emulating the Belousov-Zhabotinsky reaction as a fast subsystem and an additional circuit as a slow subsystem. We constructed a bursting oscillator circuit from two bursting cell circuit based on the hardware Oregonator with a depressing synaptic circuit. Using the simulation on program with integrated circuit emphasis (SPICE), we demonstrate that the circuit shows bursting oscillations and the bursting frequency can be regulated by tuning the depressing synapse circuit.

### **1. INTRODUCTION**

Bursting activities are often observed in neural systems at both the single cell level and the network level. In central pattern generators (CPGs) that are neural networks responsible for generating rhythmic behaviors, bursting oscillations arise from the interactions of bursting neurons [1]. Recently, it is suggested that short-term synaptic plasticity plays critical roles in such bursting oscillations in CPGs [3]-[5]. Nadim and his colleagues proposed computational models of CPGs with depressing syapse, which is a form of short-term synaptic plasticity, inspired by experimental results of the pyloric CPG of the lobster [3]-[5]. In their models, depressing synapses mediate bistability [3] and promote phase invariance [4], and regulate the frequency of bursting oscillations in CPGs [5].

In neuromorphic engineering, the output pathways of neural systems, such as CPG, have attracted much attention as well as sensory perception, recognition, and learning. Many neuromorphic engineers designed and fabricated analog CPG chips [7]-[9]. Most of these chips are difficult to regulate the operation speed because it is determined by circuit parameters physically. Focusing on the roles of the short-term synaptic plasticity in CPGs, we propose analog CMOS circuit that implements a bursting oscillator with depressing synapse. The proposed circuit is constructed form two oscillatory circuits, called the hardware Oregonator [10], and a depressing synapse circuit [11]. Using the simulation on program with integrated circuit emphasis (SPICE), we demonstrate that the circuit

shows bursting oscillations and the bursting frequency can be regulated by tuning circuit parameters in the depressing synapse circuit.

# 2. BURSTING OSCILLATOR MODEL

We here propose a bursting oscillator model with depressing synapse for analog CMOS circuit implementation.

## A. Bursting Cell Model based on the Hardware Oregonator

Bursting oscillation arises as a result of the interaction between a fast excitatory subsystem and a slow subsystem [2]. The fast excitatory subsystem has two different time-scales, i.e., it itself is a slow-fast system. As a slow-fast system, we considered the following system [2]:

$$\frac{du}{dt} = \frac{1}{\tau} \left( -u + f(u - v, \beta_u) \right) \tag{1}$$

$$\frac{du}{dt} = -v + f(u - \theta, \beta_v) \tag{2}$$

where u and v represent state variables,  $\tau$  a time constant, and  $\theta$  a threshold. The nonlinear function  $f(x, \beta)$  is given by a sigmoid function defined by:

$$f(x,\beta) = \frac{1 + \tanh(\beta x)}{2} \tag{3}$$

where  $tanh(\beta x)$  is the hypobolic tangent function, and  $\beta$  is a gain parameter. This system has originally been proposed for implementing the Oregonator model for the Belousov-Zhabotinsky (BZ) reaction system, a reaction-diffusion (RD) system, on silicon chips. Thus, the system is called the hardware Oregonator model [10].

The hardware Oregonator model has qualitatively similar dynamics to models of excitable cells, such as the Fitzhugh-Nagumo model and the Morris-Lecar model [6]. Figure 1 shows the nullclines and trajectories of both the hardware Oregonator model and the Fitzhugh-Nagumo model. These models have in common three circulative states; inactive (A), active (B  $\rightarrow$  C), and refractory periods (D  $\rightarrow$  A), as labeled in Fig. 1. Depending on the stability of the system, the hardware Oregonator shows two distinct behaviors. When the system is inactive and a fixed point of the system is unstable, it easily becomes active (A  $\rightarrow$  B) by external stimuli. Then, it turns in refractory state (C  $\rightarrow$  D). During the refractory state, the system can not be activated even if the external stimuli was

Fig. 1: Nullclines and Trajectories of hardware Oregonator model [(a) and (b)] and FitzHugh-Nagumo model [(c) and (d)].

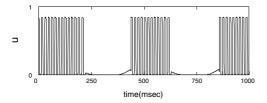

Fig. 2: Waveform of bursting cell model with periodic input.

given (excitatory mode). When a fixed point of the system is stable, the system oscillates  $(A \rightarrow B \rightarrow C \rightarrow D \rightarrow A)$  without external inputs (oscillatory mode).

For constructing a bursting cell model, we consider the hardware Oregonator model as a fast subsystem and introduce a slow subsystem represented as:

$$\epsilon \frac{dw}{dt} = -I_{leak} + I_{syn}, \ \theta = \begin{cases} \theta_{osc} & \text{if } w \ge w_{th} \\ \theta_{exc} & \text{otherwise} \end{cases}$$

(4)

where w is a slow variable,  $\epsilon$  a time constant,  $I_{leak}$  a leak current,  $I_{syn}$  a synaptic current, and  $\theta_{osc}$  and  $\theta_{exc}$  thresholds corresponding to the excitatory and oscillatory mode. We defined a burst cell model by Eqs. (1)-(4). The model shows bursting oscillations if w are varied periodically by current injection as shown in Fig. 2.

# B. Bursting Osicllator with Depressing Synapse

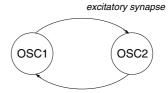

We constructed a bursting oscillator model from two bursting cell models with excitatory and inhibitory synapses as shown in Fig. 3. We defined thresholds by:

$$\theta_1 = \begin{cases} \theta_{osc} & \text{if } w \le w_{th} \\ \theta_{exc} & \text{otherwise} \end{cases}, \ \theta_2 = \begin{cases} \theta_{osc} & \text{if } w \ge w_{th} \\ \theta_{exc} & \text{otherwise} \end{cases}.$$

(5)

where  $\theta_1$  and  $\theta_2$  represent the threshold of the first and second cell, respectively. Initially, the first cell operates in the

inhibitory synapse (depressing)

Fig. 3: Configuration of bursting oscillator model.

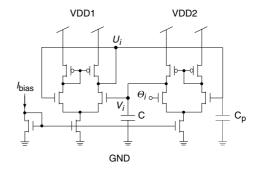

Fig. 4: Schematic of hardware Oregonator.

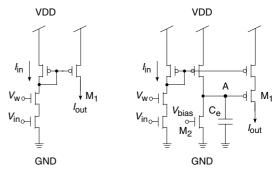

(a) conventional synapse circuit. (b) depressing synapse circuit.

Fig. 5: Schematics of synapse circuits. (a) conventional synapse circuit. (b) depressing synapse circuit.

oscillatory mode and the second cell operates in the excitatory mode. The second cell becomes the oscillatory mode through synaptic excitation with a short delay. Then, the first cell becomes the excitatory mode through synaptic inhibition, and the second cell becomes the excitatory mode in time. Thus, the bursting oscillator model shows bursting oscillation. For regulating the bursting frequency, we employ a depressing synapse as an inhibitory synapse.

#### **3. CIRCUIT IMPLEMENTATION**

We here propose analog CMOS circuit implementation of a bursting oscillator with depressing synapse.

## A. Hardware Oregonator

First, let us describe an oscillatory circuit based on the hardware Oregonator model [10]. The oscillatory circuit, called the hardware Oregonator, consists of two operationaltransconductance amplifiers (OTAs) and two capacitances as shown in Fig 4. The circuit dynamics are approximately

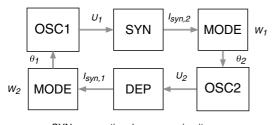

SYN: conventional synapse circuit DEP: depressing synapse circuit

Fig. 7: Schematic of mode selector.

represented as follows:

$$U = F(U-V)$$

(6)

$$C\frac{dV}{dt} = \begin{cases} I_{bias} & \text{if } V \ge \theta \\ -I_{bias} & \text{otherwise} \end{cases}$$

(7)

where U and V represent voltages,  $\theta$  a threshold voltage, C a capacitance,  $F(\cdot)$  an output voltage of an OTA, and  $I_{bias}$  a bias current. The circuit dynamics can be obtained by qualitative approximation of Eqs. (1) and (2). We assume that the variables u and v of Eqs. (1) and (2) are restricted within [0:1]. When the rate of constant of Eq. (1) is much larger than that of Eq. (2), the differential term of Eq. (1) can be neglected. Furthermore, Eq. 7 with  $\beta_v \to \infty$  forces the values of variable v to be zero when  $u \leq \theta$ , while  $v \to 1$  when  $u > \theta$ . Thus, the temporal difference in Eq. (2) can approximately be represented binary values. Consequently, we obtain the circuit dynamics represented by Eqs. (5) and (6) [10].

## B. Depressing Synapse Circuit

We employ a depressing synapse circuit that consists of a current mirror and a common-source amplifier as shown in Fig. 5(b) [11]. When the input voltage  $V_{in}$  is zero, the input current  $I_{in}$  and the voltage  $V_A$  at node A are zero. Therefore, the transistor  $M_1$  is in an on state. When  $V_{in} > 0$ ,  $I_{in}$  increases  $V_A$  and decreases the conductance of M1. If one pulse input is given, the circuit outputs a pulse current  $I_{out}$  and  $I_{in}$  charges  $V_A$ , and then the transistor  $M_2$  discharge  $C_e$  and  $V_A$  returns to zero. If pulse inputs are given at a short interval, subsequent inputs enter before  $V_A$  returns to zero, decreasing the conductance of  $M_1$  and the amplitude of  $I_{out}$ . Thus, this circuit acts as a depressing synapse circuit [11].

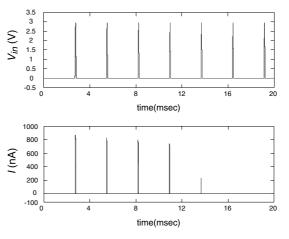

Fig. 8: Waveforms of hardware Oregonator in oscillatory mode.

Fig. 9: Output currents of depressing synapse circuit.

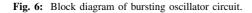

# C. Bursting Oscillator Circuit

We constructed a bursting oscillator circuit from two bursting cell circuit based on the hardware Oregonator, a depressing synapse circuit, and a conventional synapse circuit. Figure 6 shows the block diagram of the bursting oscillator circuit. We added a mode selector (Fig. 7) to the hardware Oregonator for constructing a bursting cell circuit.

### 4. SIMULATION RESULTS

We demonstrate the operation of the bursting oscillator circuit through circuit simulations. Throughout simulations, we used a circuit simulator HSPICE and the model parameters for the 1.5- $\mu$ m CMOS process.

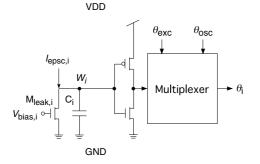

First, we show the operation of the hardware Oregonator as shown in Fig. 3. We set the capacitances at C = 10 pF and  $C_p = 0.1$  pF, the bias current at  $I_{bias} = 500$  nA, the supply voltages at VDD1=VDD2 = 3 V, and the threshold voltage at  $\theta = 0.8$  V so that the circuit operates in the oscillatory mode. Figure 8 shows the waveforms of voltages U and V in the oregonator circuit.

We show the operation of the depressing synapse circuit as shown in Fig. 4. We set the capacitance at  $C_e = 50$  pF, the supply voltages at VDD = 3.0 V, and the bias voltages at

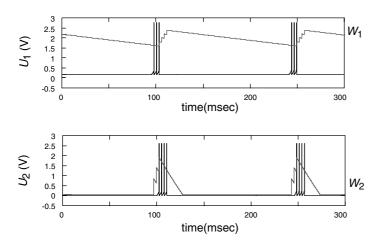

Fig. 10: Waveforms of voltages in bursting oscillator circuit (nondepressing).

Fig. 11: Waveforms of voltages in bursting oscillator circuit (depressing).

$V_{bias} = 0.38$  V and  $V_W = 1.0$  V. When a pulse train was given, the amplitude of the output current depressed (Fig. 9).

We show the operation of the bursting oscillator circuit. In the mode selectors, we set the capacitances at  $C_1 = 200 \text{ pF}$ and  $C_2 = 50 \text{ pF}$ , the bias voltages at  $V_{bias,1} = V_{bias,2} = 0.5 \text{ V}$ , and the threshold voltages at  $\theta_{osc} = 0.8 \text{ V}$  and  $\theta_{exc} = 0 \text{ V}$ . When we set the voltages at  $W_1 = 2.0 \text{ V}$  and  $W_2 = 0 \text{ V}$  as an initial condition, then the circuit shows bursting oscillation as shown in Fig. 10.

By tuning the bias voltages of the depressing synapse circuit, we can change the bursting frequency of the bursting oscillatory circuit. We set the bias voltage at  $V_{bias} = 0.35$  V. As a result of the depression of the synaptic current from the second cell to the first cell, the frequency of the slow variable  $W_1$  becomes high, and then the bursting frequency also becomes high (Fig. 11).

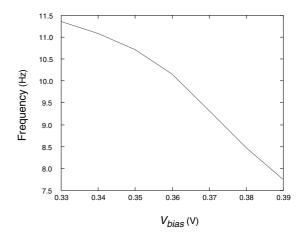

Figure 12 shows the relationship between the bias voltage of the depressing synapse circuit and the bursting frequency of the bursting oscillator circuit. This result shows that if the bias voltage becomes large, the bursting frequency monotonically decreases.

Fig. 12: Relationships between the frequency of the bursting oscillation and the bias voltages of the depressing synapse circuit.

#### 5. SUMMARY

We designed an analog CMOS circuit implementing a bursting oscillator with a depressing synapse. Bursting oscillation arises the result of interaction between a fast excitatory subsystem and a slow subsystem [2]. We employ an analog oscillatory circuit, called the hardware Oregonator, for emulating the Belousov-Zhabotinsky reaction as a fast subsystem and an additional circuit as a slow subsystem. We constructed a bursting oscillator circuit from two bursting cell circuits with a depressing synaptic circuit. Through SPICE simulations, we demonstrated that the proposed circuit shows bursting oscillations and the bursting frequency can be regulated by tuning the depressing synapse circuit. Such characteristics are suitable as a component of an analog CPG chip.

# REFERENCES

- F. Delcomyn, Foundations of Neurobiology, New York: W, H. Freeman and Co., 1997.

- [2] F. C. Hoppensteadt and E. M. Izhikevich, Weakly Connected Neural Networks, Springer-Verlag, New York, 1997.

[3] A. Bose, Y. Manor and F. Nadim, "Bistable oscillations arising from

- [3] A. Bose, Y. Manor and F. Nadim, "Bistable oscillations arising from synaptic depression", *SIAM J. App. Math.*, vol. 62, pp. 706-727, 2001.

[4] Y. Manor, A. Bose, V. Booth and F. Nadim, "Synaptic depression"

- [4] Y. Manor, A. Bose, V. Booth and F. Nadim, "Synaptic depression promotes phase invariance in a model rhythmic network," *J. Neurophysiology*, vol. 90, pp. 3513-3528, 2003.

- [5] F. Nadim, Y. Manor, N. Kopell, E. Marder, "Synaptic depression creates a switch that controls the frequency of an oscillatory circuit", in *Proc. Natl. Acad. Sci. USA*, vol. 96, pp. 8206-8211, 1999.

- [6] C. Morris and H. Lecar, "Voltage oscillations in the barnacle giant muscle fiber", *Biophysical J.*, vol. 35, pp. 193-213, 1981.

[7] S. Ryckebusch, M. Wehr, G. Laurent, "Distinct rhythmic locomotor

- [7] S. Ryckebusch, M. Wehr, G. Laurent, "Distinct rhythmic locomotor patterns can be generated by a Simple adaptive neural circuit: biology, simulation and VLSI implementation," *J. of Comp. Neuro*, vol. 1, pp. 339-358, 1994.

- [8] M. Simoni and S. DeWeerth, "Adaptation in a VLSI model of a neuron", *Trans. Circuits and Systems-II*, vol. 46, no. 7, pp. 967-970, 1999.

- [9] M. A. Lewis, M. J. Harttmann, R. Etienne-Cummings, A. H. Cohen, "Control of a robot leg with an adaptive aVLSI CPG chip," *Neurocomputing*, vol. 38-40, pp. 1409-1421, 2001.

- [10] Y. Kanazawa, T. Asai, T. Hirose, and Y. Amemiya, "A MOS circuit for bursting neural oscillators with excitable Oregonators," *IEICE Electronics Express*, vol. 1, no. 4, pp. 73-76, 2004.

- [11] Y. Kanazawa, T. Asai, and Y. Amemiya, "Basic circuit design of a neural processor: analog CMOS implementation of spiking neurons and dynamic synapses," *J. Robotics and Mechatronics*, vol. 15, no. 2, pp. 208-219, 2003.