弱反転 MOSFET を用いた温度検出スイッチ回路 萩原 淳史<sup>†a)</sup>(学生員) 廣瀬 哲也<sup>†</sup>(正員)

浅井 哲也†(正員) 雨宮 好仁†(正員)

Critical Temperature Switch Consisting of Subthreshold CMOS Circuits

Atsushi HAGIWARA $^{\dagger}$ a), Student Member, Tetsuya HIROSE $^{\dagger}$ , Tetsuya ASAI $^{\dagger}$ , and Yoshihito AMEMIYA $^{\dagger}$ , Members

# † 北海道大学大学院情報科学研究科, 札幌市

Department of Electrical Engineering, Hokkaido University, Kita 14, Nishi 9, Kita-ku, Sapporo-shi, 060–0814 Japan

a) E-mail: hagiwara@sapiens-ei.eng.hokudai.ac.jp

あらまし 特定の温度でオン状態からオフ状態に遷移する温度検出スイッチ回路を提案する.この回路は,自己パイアス電流回路の線形 MOS 抵抗が温度上昇に応じて強反転動作から弱反転動作に遷移することを利用する.回路パラメータの調節により,スイッチのしきい値温度を任意に設定可能である.

キーワード CMOS, 弱反転電流, 温度検出

# 1. まえがき

近年,情報携帯端末の普及に伴い,電子機器の小型化・高出力化が進展している.これに伴い,機器本体の性能向上だけでなく,機器の安全性・安定性対策も重要になっている.このような電子機器の安定動作を監視する対策の一つとして,電子機器の温度を監視するためにサーミスタが用いられている [1].中でも CTR素子は,温度がしきい値を超えると抵抗値が急しゅんに減少する特性をもつ.そのため過熱検知・過電流保護・温度補償に広く用いられている.これらの CTR素子は,酸化物を主体とする導電性セラミックから構成されており,材料の相転移現象による抵抗変化を利用して臨界温度の検知を行っている.

しかし、CTR素子はセラミック焼結体で構成されているため、CMOSプロセスとの適合性がなくモノリシック搭載が難しい、また、しきい値温度を自由に設定することが難しいという問題もある。そこで本研究では、MOSFETのサブスレッショルド領域の温度敏感性を利用して、CTR素子に類似した急しゅんな温度特性をもつCMOS温度検出スイッチ(Critical Temperature Switch: CTS)回路を構成する。

# 2. 回路構成·動作原理

提案する CTS 回路は , MOSFET のサブスレッショルド領域における温度特性を利用する . MOSFET のゲート・ソース間電圧 ( $V_{qs}$ ) がしきい値電圧 ( $V_{th}$ )

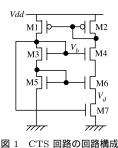

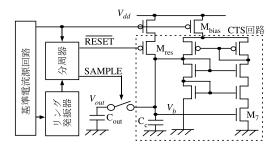

Fig. 1 Construction of CTS circuit.

以下のときサブスレッショルド電流  $I_d$  が流れる [2] . ドレーン・ソース間電圧 ( $V_{ds}$ ) が  $0.1\,\mathrm{V}$  以上のとき , ドレーン電流  $I_d$  は次の指数関数で近似できる .

$$I_d = I_0 \exp\left(\frac{V_{gs} - V_{th}}{\eta V_T}\right) \tag{1}$$

ここで, $I_0$  はサブスレッショルド電流の前置係数, $\eta$  はサブスレッショルドスロープ係数, $V_T$  ( $=k_BT/q$ ) は 熱電圧, $V_{th}$  は MOSFET のしきい値電圧である [3] ・サブスレッショルド領域で動作する MOSFET の温度 依存性を利用することで CTS 回路を構築する .

CTS 回路の構成を図 1 に示す.この回路は  $\beta$  乗算型自己バイアス回路 [4] を基本とし,抵抗に代えて線形 MOS 抵抗 M7 を用いた構成である.トランジスタ  $M1 \sim M6$  を弱反転飽和領域で動作させる.M5 と M6 のアスペクト比を K (= M6/M5) として,MOS 抵抗 M7 のドレーン電圧  $V_d$  は次式で与えられる.

$$V_d = \eta V_T \ln(K) \tag{2}$$

トランジスタ M7 のゲート電圧  $V_6$  はカスコード接続された M3 と M5 のゲート・ソース電圧の和であり,M7 のしきい値電圧より大きい値となる.したがってM7 は強反転線形領域にあり,回路を流れる電流 I とゲート電圧  $V_6$  は次式で表せる.

$$I = \beta(V_b - V_{th})V_d$$

=  $\beta(V_b - V_{th})\eta V_T \ln(K)$  (3)

$$V_b = 2V_{th} + 2\eta V_T \ln\left(\frac{I}{I_0}\right) \tag{4}$$

ここで, $\beta$  は電流利得係数である.回路を流れる電流 I とゲート電圧  $V_b$  は,式 (3) と式 (4) により相補的に 決まり,ポジティブフィードバック構成となる.この 回路では電圧  $V_b$  を出力として使用する.しきい値電 圧  $V_{th}$  は温度とともに減少し,次式で表される [2] .

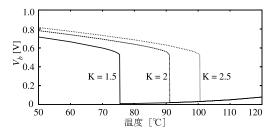

図 2 CTS 回路の動作シミュレーション . M5 と M6 の アスペクト比 K (= M6/M5) によってしきい値温度を任意設定できる .

Fig. 2 CTS circuit operation. The critical temperature can be set to a desired value by changing the aspect ratio K.

$$V_{th} = V_{th0} - \kappa T \tag{5}$$

ここで, $V_{th0}$ は絶対零度におけるしきい値電圧, $\kappa$ は しきい値電圧の温度依存係数である.式(4)の右辺第 2 項において,回路を流れる電流 I はサブスレッショ ルド前置係数  $I_0$  よりも小さくなるため対数項は負と なる.そのためIは温度とともに減少する.したがっ て , トランジスタ  $\mathrm{M7}$  のゲート電圧  $V_b$  は温度ととも に減少する.温度が回路パラメータによって定まるし きい値温度  $T_c$  を超えると , 電圧  $V_b$  は急激に低下して M7 のしきい値電圧以下となり, M7 は弱反転領域動 作に遷移する.このとき式(3)と式(4)は成立しなく なり,回路を流れる電流はほぼゼロとなる.しきい値 温度  $T_c$  前後における電圧  $V_b$  の急しゅんな変化, つま リ M7 の強反転領域動作から弱反転領域動作への遷移 を利用すれば,温度がしきい値温度 $T_c$ を超えたこと を検出するスイッチ動作を実現できる. しきい値温度  $T_c$  は回路パラメータを変化させることで任意値に設 定可能である.

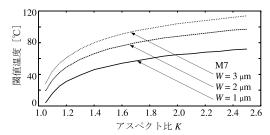

CTS 回路の動作を確認するために,SPICE シミュレーションによる検証を行った. $0.35~\mu m$ -CMOS プロセスパラメータを使用し,電源電圧を 1.5~V に設定した.図 2 は温度に対する M7 のゲート電圧  $V_b$  の変化を示す.温度の上昇とともに  $V_b$  はゆるやかに低下し,温度がしきい値温度  $T_c$  を超えると急減してほぼ 0 となる.しきい値温度  $T_c$  は M5 と M6 のアスペクト比 K を変えることで自由に設定できる.なお,線 M MOS 抵抗 M7 のチャネル幅を変えることでもしきい値温度  $T_c$  を変化させることが可能である.図 3 に,アスペクト比 K と M7 のチャネル幅 W に対するしきい値温度の変化を示す.広い範囲でしきい値温度  $T_c$  の設定が可能である.

図 3 M5 と M6 のアスペクト比 K (= M6/M5)と M7 のチャネル幅 W に対するしきい値温度の変化

Fig. 3 Threshold temperature as a function of K and W.

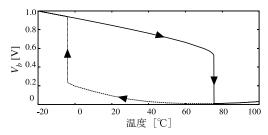

図 4 CTS 回路のヒステリシス特性 . 動作温度を上昇させ , その後下降させている . しきい値温度  $T_c=75^{\circ}\mathrm{C}$   $(K=1.5,\ \mathrm{M7};\ W/L=2\,\mu\mathrm{m}/20\,\mu\mathrm{m})$  の CTS 回路において温度下降時には温度上昇時とは異なったしきい値温度を示している

Fig. 4 Hysteretic characteristic of the CTS circuit. The CTS circuit has two threshold temperatures at which voltage  $V_b$  drops suddenly to a low value and jumps up to a high value.

#### 3. ヒステリシス特性とリセット回路

この CTS 回路は,線形 MOS 抵抗 M7 の動作が温度によって強反転パイアス条件から弱反転パイアス条件に遷移することを利用し,スイッチ動作を行っている.温度がしきい値温度  $T_c$  を超えると  $V_b$  は高い値(約  $0.6 \sim 0.7\,\mathrm{V}$ )から低い値( $0 \sim 0.1\,\mathrm{V}$ )に変化する.しかし,この回路の特性にはフィードバック作用によるヒステリシスがあり,温度の上昇時と下降時ではしきい値温度が異なる.図 4 に CTS 回路のヒステリシス特性を確認したシミュレーション結果を示す.動作温度を上昇させ,その後下降させている.ヒステリシス特性のため,温度上昇時と下降時における動作点の異なる温度領域が存在することを確認できる.

このヒステリシス特性をキャンセルするためには, ノード電圧  $V_b$  を周期的に高い値に強制設定(リセット)すればよい.そのためのリセット回路を含む CTS 回路の構成を図 5 に示す.リング発振器と分周器でリセットパルス( $\overline{RESET}$ )を発生し,そのリセットパ

図 5 リセット回路をもつ CTS 回路 Fig. 5 CTS circuit with the reset circuit.

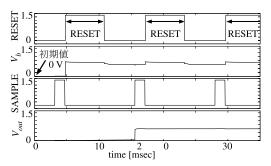

図 6 リセットつき CTS 回路 ( しきい値温度=  $75^{\circ}$ C ) の 動作 . 温度=  $70^{\circ}$ C でのシミュレーション結果 .  $V_b$  の初期電位を 0 V としている .

Fig. 6 Operation of the CTS circuit ( $T_C = 75^{\circ}$ C) with the reset circuit, simulated at  $T = 70^{\circ}$ C. The initial voltage of  $V_b$  is set to 0 V.

ルスを Mres に加えて一定時間ごとに  $V_b$  を高い値に リセットする.このリセットにより,M7 は強反転動作となる.サンプルパルス(SAMPLE)により  $V_b$  の電圧を読み出して出力電圧  $V_{OUT}$  とする.回路を安定に動作させるために,M7 のゲート端子に容量  $C_C$  を付加してある.以上の操作により,この回路のヒステリシス特性は打ち消されて,しきい値温度はただ一つ(リセット回路がないときの温度上昇時のしきい値温度と同じ値)に定まる.

上記のリセット動作を確認するために過渡解析シミュレーションを行った.ここでは,しきい値温度(=75°C)の回路を温度 $70^{\circ}$ Cで動作させる.初期条件として, $V_b$ の電圧を0VにとりM7を弱反転動作(すなわち温度 $70^{\circ}$ Cにおいて本来あってはならない状態)

とした.図 6 の動作シミュレーションで示されるように,最初のリセットパルス( $\overline{RESET}$ )によって M7 のゲート電圧  $V_b$  は強反転領域の値に復帰し,以後は正常な回路動作が実現される.なお,サンプリング信号により  $V_b$  の電圧を読み出すことで,リセットパルスとは関係なく一定の出力電圧  $V_{OUT}$  を得ることができる.リセット回路に使用したリング発振器と分周器の消費電力を削減するために,基準電流源回路 [5] ,電流制御型インバータ,及び電流制御型 NAND 回路を使用した [4] . 基準電流源回路により,約 10 nA の微小電流を生成し,その電流をインバータと NAND 回路の制御電流とすることにより低消費電力化を実現した.微小電流なので回路動作は低速であるが,温度検出スイッチ動作に支障はない.リセット回路を含む回路の消費電力は,電源電圧 1.5 V で  $1\mu$ W 以下であった.

# 4. む す び

サブスレッショルド電流の温度特性を利用した温度 検出スイッチ回路(CTS 回路)を提案した.この回路 は,温度変化により線形 MOS 抵抗の動作領域が変わることを利用し,温度がしきい値を超えるとスイッチ 動作する.設計パラメータを変更することでしきい値 温度を  $0^{\circ}$ C から  $110^{\circ}$ C まで広い温度範囲に設定できる.CTS 回路のもつヒステリシス特性については,リセット回路を付加することにより回避することができる. $0.35~\mu$ m-CMOS プロセスを使用すれば,リセット 回路を含めたすべての動作を電源電圧 1.5~V で  $1~\mu$ W 以下の極低電力動作が可能である.

# 文 献

- [1] 南任靖雄,センサと基礎技術,工学図書,1994.

- [2] Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press., 2002.

- [3] P.R. Gray and R.G. Mayer, Analysis and Design of Analog Integrated Circuits, third ed., John Wiley & Sons, 1993.

- [4] R. Baker, H. Li, D. Boyce, CMOS Circuit Design, Layout, and Simulation, IEEE Press, 1997.

- [5] H.J. Oguey and D. Aebischer, "CMOS current reference without resistance," IEEE J. Solid-State Circuit, vol.32, no.7, pp.1132–1135, 1997.

(平成18年2月1日受付,5月8日再受付)