# バラツキ補償リセット方式のCMOSイメージセンサ

応募者:加賀谷亮<sup>1</sup> 金澤雄亮<sup>1</sup> 浅井哲也<sup>1</sup> 雨宮好仁<sup>1</sup> 池辺将之<sup>2</sup> 大住勇治<sup>2</sup> 金高達也<sup>3</sup> 所属期間:1.北海道大学 2.大日本印刷㈱ 3.大日本 LSI デザイン㈱

#### 1. はじめに

近年、社会の情報化にともなって広帯域通信の分野が急速に発展している。比較的大きなデータ量を簡単に扱うことが可能となり、画像情報が頻繁にやりとりされるようになった。

画像情報の取得機器としてはデジタルカメラが大きな地位を占め、現在ほとんどの携帯電話にその機能が搭載されている。デジタルカメラの心臓部はCCDまたはCMOSのイメージセンサであり、携帯・監視モニタ・車載用機器など各種の用途に向けた開発が進んでいる。

とくに CMOS イメージセンサは周辺 CMOS 回路を同時に集積することが容易であり、同一チップ上に様々な画像処理機能を盛り込むことができて都合がよい。ただし CCD と比べて素子バラツキや熱雑音による固定パターンノイズが大きいので、その改善が課題となっている。そのため製作プロセスの改善やCDS(Correlated Double Sampling:相関2重サンプリング)等のノイズ除去法が提案され、CCD と比較して遜色のないレベルに近づいてきた。

しかし、CDS 法によるノイズ除去では、信号出力と リセット出力の差分を取るので、基本的に破壊読出し となる。そのため、蓄積途中の中間画像情報を利用 することは難しい。この中間画像情報を取得すること ができれば、蓄積中の輝度変化を読み取ることが可 能となり、様々な応用[1]への展開が期待できる。

本稿では、CMOS イメージセンサの新しいノイズ除去法として、画素セル回路にある MOSFET のしきい値バラツキをリセット時に補償する手法を提案する。この手法を用いると、撮像情報を破壊することなく中間撮像データを取得することができるので、機能的な画像処理への応用が可能となる。以下において、このリセット時ノイズ除去の方法とそのための回路構成を説明する。現在、この方法を用いた CMOS イメージセンサを設計して試作を行っている。さらに、リセット時ノイズ除去法の特徴(中間情報が取得できること)を活かした応用の一例——画素出力の飽和時間予測による広ダイナミックレンジ化——についても説明する。

### 2. バラツキ補償リセットを行う画素回路

#### 2.1. 画素回路の MOS しきい値バラツキ

CMOS イメージセンサでは、画素セルの回路に使う MOSFET のしきい値バラツキによって、以下のように固定パターンノイズを生じる。

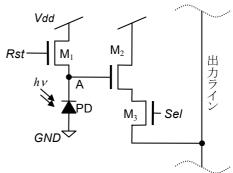

一般的な画素セルの回路(3Tr型 Active pixel sensor)を図1に示す。撮像サイクルのはじめに Rst信号で MOSFET M1をオンにしてフォトダイオード(PD)を充電する(リセット)。A点の電位は Vddとなる。フォトダイオードに光が当たると光電流が流れて充電電荷が放電される。このとき A点の電位が光強度に応じて低下する。その電位を M2のソースフォロアで取り出す。画素セルの選択は M3で行なう。これに Sel信号を与えることで、画素セルの出力電位を出力ラインに読み出すことができる。読み出し後に再びリセットを行なって次の撮像サイクルを繰り返す。

図1 一般的な CMOS イメージセンサの画素回路

この回路の主な問題点は、M2にしきい値バラツキがあると、それが信号出力に現れて固定パターンノイズの主な原因となることである。そして MOSFET を集積するとき、同一チップ上であっても、しきい値にバラツキを生じることは避けられない。この固定パターンノイズを除去するため、CDS 法では信号を出力した後にその画素回路をリセットし、信号出力とリセット出力の差分をとってしきい値バラツキを補正している。

# 2.2. しきい値バラツキを補償する画素回路

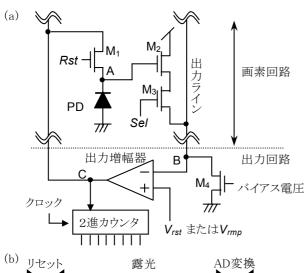

CDS 法によらずに MOSFET のしきい値バラツキを 補正するため、新しい画素回路を提案する。その構 成を図2に示す。画素セルと高利得の出力増幅器と の間で負帰還ループ回路を構成することに特徴がある。出力増幅器は一つの画素列(出力ライン1本)あたり1個あればよい。

この回路は以下のように動作する。出力増幅器の非反転入力には一定電圧 Vrst を与えておく。撮像サイクルのはじめに Rst 信号で M1をオンにしてフォトダイオード (PD)を充電する。同時に Sel信号で M3をオンにして、画素回路と出力増幅器の間に負帰還ループを形成する。この負帰還によって、出力ラインの電位 (B点の電位)は M2のしきい値バラツキによらず Vrst と等しくなる。言い換えると、M2のしきい値バラツキに応じてフォトダイオードの充電電位 (A 点の電位)が調節され、出力ラインの電位は常に Vrst にリセットされる。この動作によって MOSFET のしきい値バラツキを補償できる。

このバラツキ補償リセットの後に M1と M3をオフに する。フォトダイオードの光電流で充電電荷が放電されて A 点の電位が低下する。その電位を M2のソースフォロアで出力ラインに取り出すことは従来の画素 回路と同様である。

図2 バラツキ補償リセット方式の画素回路

(a)画素セルと出力部の回路構成, (b) 制御信号と信号電圧のタイミング。蓄積時間(33 ms)と比べてリセット時間と AD変換時間は非常に短い(1  $\mu$ s~数 $\mu$ s)。

#### 2.3. 画素信号の AD 変換

Sel 信号で M3をオンにすると出力ラインに画素信

号が現れる。その電圧をディジタル信号に変えて外部に取り出す。そのために、出力増幅器の非反転入力を一定電圧 Vrst からランプ電圧 Vrmp に切り替える。同時に、クロックを入力とする2進カウンタを動作させる。出力増幅器はコンパレータとして働き、画素信号の電圧値を PWM 変換した信号パルスを図2(a)のC点に出力する。この信号パルスでカウンタを停止させ、そのときのカウンタの計数値をバイナリディジタル出力として取り出す。

出力増幅器には普通の演算増幅器を用いるが、ただし位相補償容量の接続を制御信号でオンオフできるように構成する。すなわち、負帰還ループでバラツキ補償リセットを行うときは位相補償容量を接続して発振を防止する。ランプ電圧により AD 変換を行うときは、位相補償容量を切り離してスルーレートの大きいコンパレータとして動作させる。この操作によって、一つの演算増幅器を負帰還リセットと PWM 変換の両方に使い分けることができる。

#### 2.4. 回路の動作(シミュレーション)

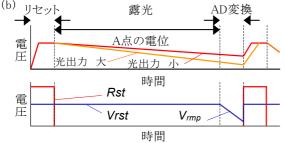

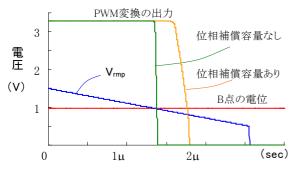

$0.25 \mu m$  CMOS のパラメータを用いて回路を設計した。HSPICE による動作シミュレーションの例を<u>図3</u>と図4に示す。

図3はバラツキ補償リセットの動作である。一例としてリセット目標値 Vrst=1 Vに設定し、時間 t=0 でリセットを開始した。なおフォトダイオードの初期電圧は 0 とした。ソースフォロアトランジスタ M2のしきい電圧値 Vth=300 mV と Vth=600 mV の場合について、出力ラインの電圧を時間の関数として図示してある(実際にはしきい値がこれほどバラつくことはない)。およそ 100 ns でリセットが終了し、出力ライン電圧のバラツキは 0.1 mV 以内の微小範囲に収まる。

図3 バラツキ補償リセットの動作のシミュレーション

図4は出力増幅器で画素信号を PWM 変換したときの出力パルス波形である。出力増幅器に位相補償容量がある場合とない場合を比較して示した。ランプ電圧が出力ライン電圧より低くなったときに PWM パルスがゼロとなり、画素信号の電圧がパルス幅に変

換される。出力増幅器の応答を速くして正確な PWM 変換を行うためには、位相補償容量を切り離すことが不可欠である。

図4 PWM 変換出力の波形 (シミュレーション)

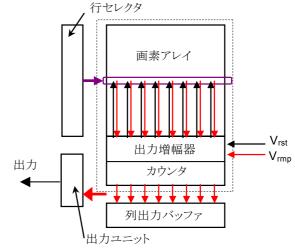

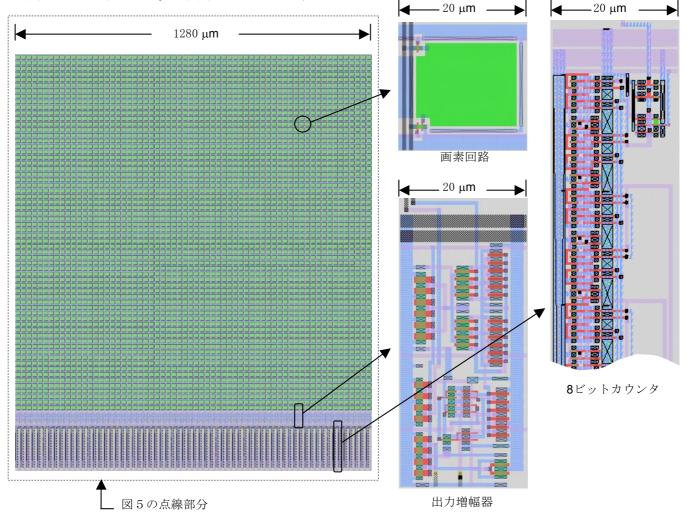

#### 3. イメージセンサの設計

提案した画素回路を搭載した CMOS イメージセン サを設計した。画素数 64×64のプロトタイプチップで ある。その全体構成を<u>図5</u>に示す。画素アレイと出力 増幅器/カウンタの他に、行選択のためのセレクタと 列出力のバッファを持つ。画素出力を8ビットディジ

タル出力に変換し、それを出力回路で時系列信号に直して出力する。画素アレイ/出力増幅器/カウンタの部分のレイアウトパターンを図6に示す。

図5 設計したイメージセンサの全体構成

図 6 画素アレイ/出力増幅器/カウンタのレイアウトパターン(他の回路を含めたチップ全体は 3.3×3.3mm²)

# 4. 広ダイナミックレンジへの応用

#### 4.1 中間測定による露光時間の調節

本稿で提案した画素回路では、画素出力を非破壊で中間測定して飽和時間を予測できる。この特徴を利用すると、画素回路の出力ダイナミックレンジを擬似的に拡大することが可能となる。その方法を以下に述べる。現在この方法による拡大ダイナミックレンジの CMOS イメージセンサを設計中である。

提案する方法の要点は「画素出力を中間測定して入射光の強度を推測し、必要に応じて中間リセットを行って露光時間を調節する」ということにある。次に動作の具体例を説明する。

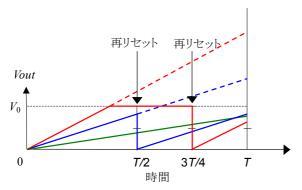

いま説明のために、画素回路の出力電圧 Vout の範囲を 0(入射光なし)から  $V_0$ (強い入射光での飽和値)までと考える(実際の出力電圧はそうではないが説明上は差し支えない)。また、個々の画素回路からフレーム時間 Tごとに出力を取り出すとする。いま例として、ダイナミックレンジを擬似的に 4 倍拡大する操作を次に示す(図7)。

- (1) 画素回路を時刻 = 0 でリセットする。このリセット で MOSFET のしきい値バラツキが補正される。

- (2) 時刻 T/2 で中間読み出しを行う。この出力 Vout を出力増幅器で  $V_0/2$  および  $V_0$  と比較する。

- (3)  $Vout < V_0/2$  ならば出力は飽和しないと予測して そのまま蓄積を続行し、時刻 Tで最終出力を読み出す (図7の緑線, 露光時間は T)。

- (4)  $V_0/2$  <  $V_0$  ならば時刻 T では出力が飽和すると予測できる。そこで即時に再リセットを行い、その後に時刻 T で最終出力を読み出す(図7の青線,露光時間は T/2)。

- (5)  $Vout = V_0$  のときはすでに飽和しているので、露光時間をさらに短縮するため時刻 3T/4 で再リセットし、時刻 T で最終出力を読み出す(図7の赤線,露光時間は T/4)。

図6 画素出力の中間測定による露光時間の調節

なお、露光時間の情報は各画素ごとに外部メモリに記憶する。以上の操作によってダイナミックレンジを 擬似的に4倍拡大できる。さらに拡大したいときには 中間測定による予測回数を増やす。すなわち、中間 測定をn 回(測定時刻は $T/2^n$ , $T/2^{n-1}$ ,...,T/2)行って露光時間を調節することで、ダイナミックレンジを  $2^{n+1}$  倍に拡大できる。

フレーム時間 T の後、画素の出力を AD 変換してディジタル出力とする(8 ビット出力を想定)。露光時間が  $T/2^n$  のときには、画素出力の実データは露光時間情報と合わせて(8 ビットディジタル出力)  $\times 2^n$ で表すことができる。そのため、実データはディジタル出力をビットシフトするだけで得られる。一例として画素出力 110010111,露光時間 T/4 のとき、実データは2 ビット左シフトして 1100101100 となる。

現在設計を進めている拡大ダイナミックレンジ型イメージセンサは、n = 3 として 16 倍のダイナミックレンジ向上を行うものである。なお各画素を独立にリセットできるように、図2の構成に少し変更を加えてある。

#### 4.2. 画像データの出力形式

前節のように広ダイナミックレンジ化された画素出力データは、実際に使う画像表示形式と異なりビット数が拡張されている。そこで、標準の出力ビット数(ここでは8ビット)に合わせた圧縮変換が必要となる。しかし単純に線形変換を行うと、広ダイナミックレンジ画像の特徴が失われてしまう可能性がある。そこで「画像全体の輝度統計にあわせて各露光時間ごとにビット圧縮率を調節する」ことを考えた。

画像全体の露光時間情報は T/2 で求めることができる。したがって圧縮変換は残りの T/2 時間で行うことができる。変換アルゴリズムの概要は以下のとおりである。

- (1) 画像全体で各露光時間 (露光時間 T/2"ごと)の 画素数の割合を求める。なお露光時間 Tの画素数は 2 倍の重みをつける。

- (2) 画素数の割合をもとに、各露光時間でのデータに対する圧縮率を算出する。画素数の割合が大きい露光時間でのデータは圧縮率を小さくして階調数を多く割り当てる。割合が小さい露光時間のデータは階調数を小さくして圧縮率を大きくとる。画像全体では8ビット階調とする。

このデータ圧縮率の算出は、時間的に余裕があるので、加算器による簡易除算で行うことができる(シフト演算と減算を逐次的に繰り返す)。

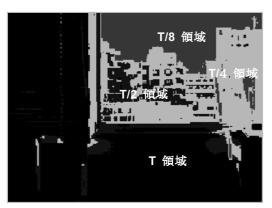

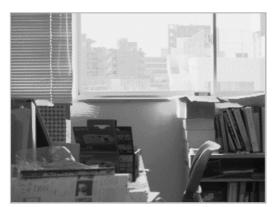

以上のアルゴリズムによる広ダイナミックレンジ化の効果を<u>図8</u>に示す(シミュレーション結果)。図8(a)は全画素で露光時間を同一にとった普通の撮像画

像の例である。晴天時に室内を撮影したもので、窓の外が明るいため白とびを生じている。これに対して、提案した手法では、はじめに各画素の光入力に応じて露光時間ごとの画素数の割合を求め、それに対応させて画素出力データを8ビットに圧縮する。こうして得られた広ダイナミックレンジ画像を図8(c) に示す。室内の画像をそのまま鮮明に保ちながら、明るい窓の外の景観も表現できている。

(a) 従来の撮像画像:晴天時に室内を撮影

(b) 画像への露光時間の割り当て

(c)本方式による広ダイナミックレンジ画像

図8 露光時間の調節による広ダイナミックレンジ化

#### 4. むすび

CMOS イメージセンサの新しいノイズ除去法として、 画素セル回路の MOSFET のしきい値バラツキをリセット時に補償する方法を提案した。この方法によれば、 画素の撮像データを破壊することなく蓄積途中で参照できるので、さまざまな画像処理に応用することができる。現在この方法を用いた CMOS イメージセンサを設計して試作を行っている。

さらに、中間情報を非破壊で取得できる特徴を活かした広ダイナミックレンジ化の方式もあわせて提案した。この方式による CMOS イメージセンサを設計中であり、光量比の大きい対象物の観測・監視システム等への応用展開を考えている。

# 文 献

(1) D. Handoko, 川人祥二, 田所嘉昭, 松澤昭, "高速非破壊中間画像 CMOS イメージセンサの設計 と試作,"映像メディア学会誌, Vol.55, No.2, pp.264-270(2001).