PAPER Special Section on Analog Circuits and Related SoC Integration Technologies

# **High-Resistance Resistor Consisting of a Subthreshold CMOS Differential Pair**

Shin'ichi ASAI<sup>†a)</sup>, Ken UENO<sup>†</sup>, Student Members, Tetsuya ASAI<sup>†</sup>, and Yoshihito AMEMIYA<sup>†</sup>, Members

**SUMMARY** We propose a CMOS circuit that can be used as an equivalent to resistors. This circuit uses a simple differential pair with diodeconnected MOSFETs and operates as a high-resistance resistor when driven in the subthreshold region of MOSFETs. Its resistance can be controlled in a range of 1–1000 MΩ by adjusting a tail current for the differential pair. The results of device fabrication with a 0.35- $\mu$ m 2P-4M CMOS process technology is described. The resistance was 13 MΩ for a tail current of 10 nA and 135 MΩ for 1 nA. The chip area was 105  $\mu$ m × 110  $\mu$ m. Our resistor circuit is useful to construct many high-resistance resistors in a small chip area.

key words: CMOS, integrated circuit, resistor, high resistance, differential circuit, subthreshold

#### 1. Introduction

In integrated circuits, high resistances cannot be used easily because they require very large areas on a chip. However, using high-resistance resistors makes it easier to construct many circuits and to develop ICs with new functions. In this paper, we propose making an equivalent of a high-resistance resistor with a CMOS circuit. We will be able to make  $1-1000 \text{ M}\Omega$ -resistors in a small chip area.

In CMOS integrated circuits, resistors are usually made using doped polysilicon layers. However, polysilicon resistors need a very large area to create large resistances. As an example, for a 100 M $\Omega$  resistor, we have to tolerate a large area of 0.5 millimeter square even if we use a 1–2 k $\Omega$ /square high-resistance poly layer. Using far lightly doped polysilicons can make larger resistances, but it leads to very low accuracy and large temperature dependence of resistance. In addition, polysilicon resistors are not convenient for applications that need variable resistances.

To solve these problems, we propose a concise CMOS circuit that operates as a high-resistance resistor. With this circuit we can achieve 100 M $\Omega$  resistance within a small area, when the differential pair is operated in the subthreshold region, that is, the region that the gate-source voltage for the MOSFET is lower than its threshold voltage (see [1] for subthreshold operation of MOSFETs). The high-resistance device can be controlled the resistance by the tail current of a differential pair. Several CMOS circuits equivalent to resistors have previously been reported [2]–[5], but they all have a complicated construction with many MOSFETs. In

Manuscript received October 5, 2009.

Manuscript revised January 15, 2010.

<sup>†</sup>The authors are with the Department of Electrical Engineering, Hokkaido University, Sapporo-shi, 060-0814 Japan.

a) E-mail: s\_asai@lalsie.ist.hokudai.ac.jp

DOI: 10.1587/transele.E93.C.741

contrast, our resistor circuit consists of a simple differential pairs with a small area and operates as an equivalent to  $1-1000 \text{ M}\Omega$  resistors.

The following provides the details on our resistor circuit. We first show the construction and operation of our resistor circuit. We then describe the fabrication and measurement of the circuit. As an application, we make a CR phase-shift oscillator using our resistor circuits. Finally, we present a method of compensating for the temperature dependence of our circuit.

# 2. Structure of Resistor Circuit

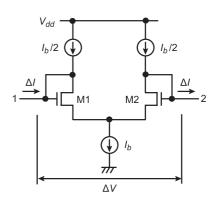

Figure 1 illustrates the principle of our resistor circuit. The circuit uses a diode-connected differential pair (M1, M2) driven by tail current  $I_b$ . The load currents (denoted by  $I_b/2$ ) are fixed to half the tail current. In this circuit, given a voltage  $\Delta V$  between terminals 1 and 2, a current  $\Delta I$  flows into terminal 1 and an equal current  $\Delta I$  flows out of terminal 2. This current  $\Delta I$  is proportional to  $\Delta V$  if the differential pair is operated in its linear region. The circuit therefore operates as a resistor with terminals 1 and 2.

If the circuit is operated in the subthreshold region (weak inversion) of MOSFETs [6], drain current  $I_D$  in the MOSFET is given by,

$$I_D = \frac{I_b}{2} = \frac{W}{L} I_0 \exp\left(\frac{q(V_{GS} - V_{th})}{mkT}\right)$$

$$\cdot \left(1 - \exp\left(-\frac{qV_{DS}}{kT}\right)\right), \qquad (1)$$

$$I_0 = \mu C_{ox}(m-1) \cdot \left(\frac{kT}{q}\right)^2,$$

Fig. 1 Differential circuit equivalent of a resistor with terminals 1 and 2.

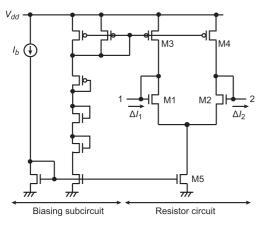

Fig. 2 Resistor circuit with biasing subcircuit. Aspect ratio is  $20 \,\mu\text{m}/4 \,\mu\text{m}$  for every MOSFET.

where W/L is the aspect ratio of the transistor,  $\mu$  is the carrier mobility,  $C_{ox}$  is the gate-oxide capacitance, m is the subthreshold slope factor, k is the Boltzmann constant, q is the elementary charge,  $V_{GS}$  is the gate-source voltage,  $V_{th}$  is the threshold voltage,  $V_{DS}$  is the drain-source voltage of a MOS-FET, and T is temperature. For  $V_{DS} > 0.1$  V,  $I_D$  is given by

$$I_D = \frac{I_b}{2} = \frac{W}{L} I_0 \exp\left(\frac{q(V_{GS} - V_{th})}{mkT}\right).$$

(2)

For a voltage  $\Delta V$  between terminals 1 and 2 of the differential pair, the current in transistor M1 is given by

$$\frac{I_b}{2} + \Delta I = \frac{W}{L} I_0 \exp\left(\frac{q(V_{GS} - V_{th} + \Delta V/2)}{mkT}\right)$$

$$= \frac{I_b}{2} \exp\left(\frac{q\Delta V}{2mkT}\right). \tag{3}$$

For  $q\Delta V/(2mkT) \ll 1$ , Eq. (3) can be rewritten as

$$\frac{I_b}{2} + \Delta I = \frac{I_b}{2} \exp\left(1 + \frac{q\Delta V}{2\,mkT}\right).\tag{4}$$

If the circuit is driven in the subthreshold region, the resistance is given by

$$R = \frac{\Delta V}{\Delta I} = \frac{4 \, mkT}{qI_b}.\tag{5}$$

For instance, we can easily make a 100 M $\Omega$  resistor using a 1-nA tail current. The resistor characteristic is linear for  $-mkT/q < \Delta V < mkT/q$ .

Figure 2 shows the entire configuration of our resistor circuit with a biasing subcircuit. We provide the tail current and the load current for the differential pair (M1-M5) using a bias current  $I_b$ . We set  $I_b$  to 100 nA or less to operate M1-M4 in the subthreshold region.

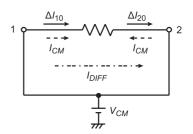

In actual circuits, offset currents occur due to imbalances between MOSFETs in the circuit. In other words, currents flow through the resistor even if voltage  $\Delta V$  between the resistor's terminals 1 and 2 is 0, as shown in Fig. 3. These offset currents  $\Delta I_{10}$  and  $\Delta I_{20}$  comprise two components, i.e., (i) common-mode offset current  $I_{CM}$  that flows

**Fig. 3** Offset currents of resistor circuit. Offset currents  $\Delta I_{10}$  and  $\Delta_{I20}$  consist of common-mode offset current  $I_{CM}$  and differential offset current  $I_{DIFF}$ .

into both resistor terminals, and (ii) differential offset current  $I_{DIFF}$  that flows from terminal 1 to terminal 2. They are given by

$$\Delta I_{10} = I_{DIFF} + I_{CM},\tag{6}$$

$$\Delta I_{20} = I_{DIFF} - I_{CM}.\tag{7}$$

Common-mode offset  $I_{CM}$  occurs if the currents ratio of M5 to M3 and M4 is not 2:1. Differential offset  $I_{DIFF}$  occurs if currents in M1 and M3 or currents in M2 and M4 are not equal to each other. The offset currents affect the resistance characteristic as follows.

#### 3. Operation of Resistor Circuit

We made the resistor circuit, using a 0.35- $\mu$ m 2P-4M CMOS process technology. The aspect ratio of MOSFETs was set to 20  $\mu$ m/4  $\mu$ m for all transistors. The tail current of the differential pair was almost equal to bias current  $I_b$ . The size of the circuit was 105  $\mu$ m × 110  $\mu$ m. (The photograph of the resistor circuit is shown in Fig. 9, which is given later for the explanation of the CR phase-shift oscillator that uses the resistor circuits.)

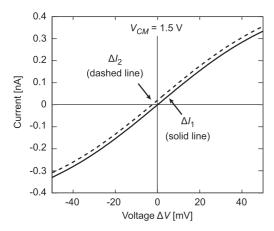

Figure 4 shows the voltage-current  $(\Delta V - \Delta I)$  curve of the resistor circuit, measured for power supply  $V_{dd} = 3$  V, common-mode voltage  $V_{CM} = 1.5$  V for terminals 1 and 2, and bias current  $I_b = 1$  nA. The characteristic was almost linear for voltages from -40 mV to 40 mV. In this range, the device can be used as a resistor. The resistor circuit has two differences compared to a true resistor. That is, (a) the voltage-current curve does not pass the zero point, and (b) current  $\Delta I_1$  (solid line) flowing into terminal 1 is not exactly equal to current  $\Delta I_2$  (dashed line) flowing out of terminal 2. This results from the offset currents.

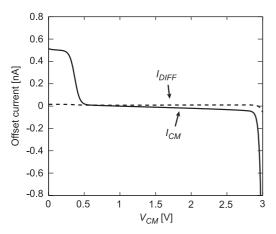

Figure 5 shows the common-mode offset current  $I_{CM}$  (solid line) and the differential offset current  $I_{DIFF}$  (dashed line) as a function of common-mode voltage  $V_{CM}$ , measured for  $V_{dd} = 3 \text{ V}$ ,  $I_b = 1 \text{ nA}$ . In this example, for a  $V_{CM}$  in a 0.4–2.8 V range, the common-mode offset current and the differential offset current are small, so the circuit can be used as a resistor.

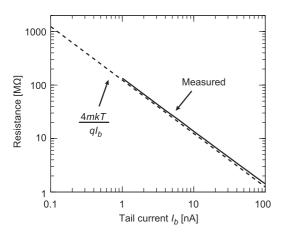

Figure 6 shows the resistance as a function of tail current  $I_b$ . The solid line is the measured result and the dashed line is a theoretical value calculated from Eq. (5). The resistance was inversely proportional to bias current  $I_b$ , so we were able to control the resistance with  $I_b$ . For example, the

**Fig. 4** Voltage-current characteristic of resistor circuit, measured for  $I_b$  = 1 nA,  $V_{dd}$  = 3 V, and  $V_{CM}$  (common-mode voltage for terminals 1 and 2) = 1.5 V.

**Fig. 5** Common-mode offset current  $I_{CM}$  and differential offset current  $I_{DIFF}$  as a function of common-mode voltage  $V_{CM}$  for terminals 1 and 2, measured for  $I_b = 1$  nA and  $V_{dd} = 3$  V.

**Fig.6** Resistance of resistor circuit as a function of bias current  $I_b$ . Sold line shows measured data, and dashed line shows theoretical resistance.

resistance at room temperature was  $135 \text{ M}\Omega$  for  $I_b = 1 \text{ nA}$ and  $13 \text{ M}\Omega$  for  $I_b = 10 \text{ nA}$ .

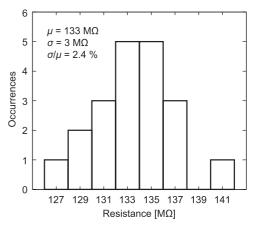

Figure 7 shows the distribution of the resistance for 20 samples measured for  $I_b = 1$  nA,  $V_{dd} = 3$  V, and  $V_{CM} = 1.5$  V.

**Fig.7** Distribution of resistance for 20 samples measured at room temperature.

The mean value of the resistance was 133 M $\Omega$ , and the standard deviation was 3 M $\Omega$ . The process sensitivities  $\sigma/\mu$  ( $\mu$  = mean value,  $\sigma$  = standard deviation of the distribution) was 2.4%, so the effect of process variations was small.

# 4. Application — CR Phase-Shift Oscillator

#### 4.1 Circuit Configuration

As an application for our resistor circuit, we made a CR phase-shift oscillator, using a phase-shift circuit comprising a number of our resistor circuits and a number of capacitors in combination with an inverting amplifier.

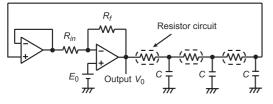

Figure 8 depicts the oscillator configuration in which the resistor circuits are shown as a resistors circled by dashed lines.

The gain G of the CR phase shifter in Fig. 8 is given by

$$G = 1 - 5R^2\omega^2 C^2 - jR\omega C(R^2\omega^2 C^2 - 6),$$

(8)

where *R* is the resistance of the resistor circuits, *C* is the capacitance combined with the resistor circuits, and  $\omega$  is angular frequency. The oscillator operates at a frequency that makes the imaginary part of G zero (i.e., the phase shift is  $\pi$ ). That is,

$$\omega = \frac{\sqrt{6}}{CR},\tag{9}$$

and therefore the oscillation frequency is

$$f = \frac{\sqrt{6}}{2\pi CR}.$$

(10)

Therefore, we can control oscillation frequency f by adjusting bias current  $I_b$  because the resistance R of the resistor circuit is given by  $R = 4mkT/(qI_b)$ . (The frequency characteristic of the resistor circuit is shown in Appendix.)

#### 4.2 Measurement Results

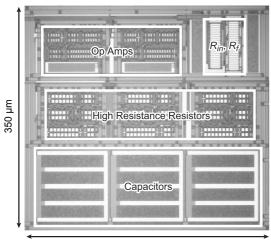

Figure 9 shows the chip photograph of CR phase-shift oscillator fabricated using a 0.35-µm 2P-4M CMOS process

Fig. 8 CR phase-shift oscillator. Resistors circled by dashed lines represent resistor circuits.

370 µm

**Fig. 9** Chip photograph of phase-shift oscillator. Chip size is  $350 \,\mu\text{m} \times 370 \,\mu\text{m}$ . Parameters used were  $R_{in} = 5 \,\text{k}\Omega$ ,  $R_f = 170 \,\text{k}\Omega$ ,  $C = 10 \,\text{pF}$ ,  $V_{dd} = 3 \,\text{V}$ , and  $E_0 = 1.5 \,\text{V}$ .

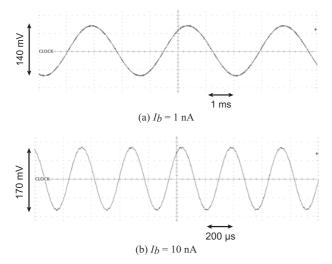

**Fig. 10** Output waveforms of phase-shift oscillator, measured for two bias current  $I_b$  values for resistor circuit.

technology. The chip area was  $350 \,\mu\text{m} \times 370 \,\mu\text{m}$ . The input and feedback resistances for the inverting amplifier were  $R_{in}$ = 5 k $\Omega$  and Rf = 170 k $\Omega$ . Figure 10 shows measured oscillation waveforms for the output node (output  $V_0$  in Fig. 8). For example, a parameter set of  $V_{dd}$  = 3 V,  $E_0$  = 1.5 V, and C = 10 pF produced a frequency of 2.8 kHz for  $I_b$  = 10 nA and 290 Hz for  $I_b$  = 1 nA. Because the voltage swing of output  $V_0$  was larger than 100 mV, the resistor circuit in the first stage of the phase shifter was out of the linear operation. So the resistance of the first stage was larger than theoretical value. Therefore, the oscillation frequency was by -7% lower than we had expected. Our resistor circuit can provide a high resistance easily, so we can use it to build sine-wave oscillators for very low frequency applications.

#### 5. Temperature Compensation of the Resistor Circuit

#### 5.1 Using PTAT Current Source

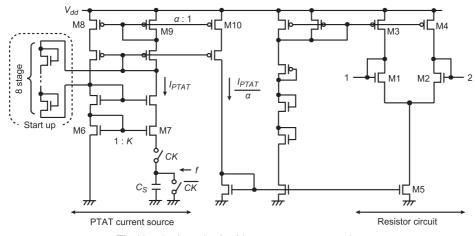

The resistance of our circuit is given by  $4mkT/(qI_b)$  and is therefore proportional to temperature for a constant tail current. To cancel this temperature dependence, we designed an improved circuit that used a Proportional To Absolute Temperature (PTAT) current as the tail current.

Figure 11 shows the circuit using the PTAT current source as the bias circuit. The PTAT current source forms a  $\beta$  multiplier self bias circuit consisting of current mirrors (M6, M7, M8, M9 and other four transistors) and a switched-capacitor resistor ( $C_S$  and CK and  $\overline{CK}$ ) [7]. Every MOSFET has the same aspect ratio, but M7 alone has an aspect ratio K times larger than those of other MOSFETs. The subcircuit circled by a dashed line is a start-up circuit to drive the PTAT current source. This subcircuit makes a transient current path from  $V_{dd}$  to ground through M9 and M6, thereby ensuring that the PTAT current source voltage  $V_{GS6}$  in M6 is equal to the sum of the gate-source voltage  $V_{GS7}$  in M7 and the voltage drop  $I_{PTAT}R_S$  across the switched-capacitor resistor, and is given by

$$V_{GS6} = V_{GS7} + I_{PTAT}R_S,$$

$$R_S = \frac{1}{C_S f},$$

(11)

where  $R_S$  is the resistance of the switched-capacitor resistor ( $C_S$  is the switching capacitance and f is the switching frequency). Equation (11) can be written as

$$I_{PTAT}R_S = V_{GS6} - V_{GS7} = \frac{mkT}{q} \ln\left(\frac{I_D}{I_0} \cdot \frac{L}{W}\right) + V_{th6}$$

$$-\frac{mkT}{q} \ln\left(\frac{I_D}{I_0} \cdot \frac{L}{WK}\right) - V_{th7} = \frac{mkT}{q} \ln K, \quad (12)$$

where *K* is the aspect ratio of M6 to M7. If the MOSFETs are operated in the subthreshold region, the PTAT current  $I_{PTAT}$  is given by

$$I_{PTAT} = \frac{mkTC_{S}f}{q}\ln K.$$

(13)

If we set aspect ratio of M9 and M10 to  $\alpha$  : 1, the tail current of the circuit is  $I_{PTAT}/\alpha$ . Therefore, the theoretical resistance between terminals 1 and 2 is given by

$$R = \frac{4\alpha}{C_{\rm S}f\ln K}.\tag{14}$$

In this way, we can obtain a temperature-independent resistance.

Fig. 11 Resistor circuit with temperature compensation.

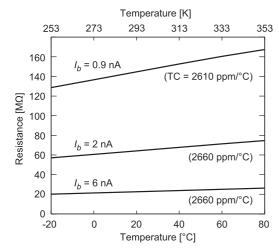

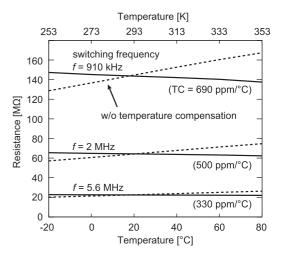

Fig. 12 Temperature dependence of resistor circuit for three bias currents.

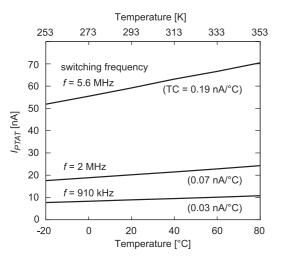

Fig. 13 Temperature characteristic of PTAT current source for three switching frequencies.

# 5.2 Simulation Results

We simulated the temperature dependence, using a set of

Fig. 14 Temperature characteristic of resistor circuit with compensation. Parameters used for fabrication were  $V_{dd} = 3 \text{ V}$ ,  $\alpha = 10$ , K = 2, and  $C_S = 0.55 \text{ pF}$ .

$0.35 \,\mu$ m-CMOS device parameters. First, Fig. 12 shows the temperature dependence of the resistance without temperature compensation (i.e., the circuit shown in Fig. 2). The temperature coefficient (TC) was in the 2610–2660 ppm/°C range for a tail current of 0.9–6 nA.

Then, we simulated the improved circuit shown in Fig. 11. Figure 13 shows the temperature dependence of the PTAT currents  $I_{PTAT}$  for three switching frequencies, with  $C_S = 0.55$  pF. The current changed linearly with temperature. Figure 14 shows the temperature dependence of the resistance in the improved circuit. The temperature coefficient was 330–690 ppm/°C for resistances from 20–140 M $\Omega$ . In this way, we were able to obtain high-resistance resistors with a small temperature coefficient.

#### 6. Conclusion

We proposed a resistor circuit to make a high-resistance resistor with a small area. This circuit uses a CMOS differential pair driven in the subthreshold region. A prototype chip was formed and the efficiency of its operation was confirmed. The circuit makes it easy to achieve the equivalent of a high-resistance resistor of 1–1000 MΩ. As a circuit application, we fabricated a CR phase-shift oscillator using our resistor circuits and observed that its oscillation frequency was as expected. A method of compensating for the temperature dependence of this resistor circuit was also presented and it was confirmed that a small temperature dependence of resistance could be achieved by using a PTAT current as a tail current of the resistor circuit. We are now developing an improved resistor circuit that has a wider voltage range of linear operation and a lower offset current value.

# Acknowledgments

This work was supported by the University of Tokyo's VLSI Design and Education Center (VDEC) in collaboration with Cadence Design Systems, Inc.

#### References

- A. Wang, B.H. Clhoun, and A.P. Chandracasan, Sub-Threshold Design for Ultra Low-Power Systems, Springer, New York, 2006.

- [2] K. Nagaraj, "New CMOS floating voltage-controlled resistor," Electron. Lett., vol.22, no.12, pp.667–668, June 1986.

- [3] S.P. Singh, J.V. Hanson, and J. Vlach, "A new floating resistor for CMOS technology," IEEE Trans. Circuits Syst., vol.36, no.9, pp.1217–1220, Sept. 1989.

- [4] G. Wilson and P.K. Chan, "Novel voltage-controlled grounded resistor," Electron. Lett., vol.25, no.25, pp.1725–1726, Dec. 1989.

- [5] S. Sakurai and M. Ismail, "A CMOS square-law programmable floating resistor independent of the threshold voltage," IEEE Trans. Circuits Syst. II, vol.39, no.8, pp.565–574, Aug. 1992.

- [6] Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices, Cambridge Univ. Press, U.K., 2002.

- [7] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill Companies, New York, 2001.

#### Appendix

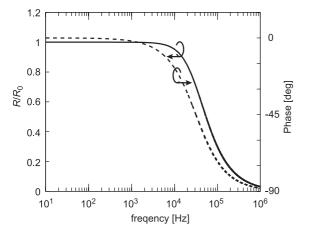

Figure A  $\cdot$  1 shows frequency dependence of the resistance, calculated for  $I_b = 1$  nA. At high frequencies, the resistance

Fig. A 1 Frequency characteristic of resistor circuit.

is a complex number expressed by  $R \exp(j\theta)$ . The figure shows *R* normalized to dc resistance  $R_0$ , and phase  $\theta$  as a function of frequency. This result shows that the circuit can be used as a resistor in a frequency range of 0–10 kHz.

Shin'ichi Asai was born in Tottori, Japan in 1986. He received the B.S., degrees in the Department of Electrical and Electronic Engineering from Muroran Institute of Technology, Muroran, Japan, in 2008. He is currently working toward the M.E., degree in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His current research interest is in analog CMOS circuits.

Ken Ueno received the B.S. degree in the Department of Electronics and Information Engineering, Hokkai-Gakuen University, Sapporo, Japan, in 2002, and the M.S. degree in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan, in 2007, where he is currently working toward the Ph.D. degree. His current research interests are in PVTtolerant ultra-low-power analog CMOS circuits. Mr. Ueno is a member of IEEE.

**Tetsuya Asai** received the B.S. and M.S. degrees in electrical engineering from Tokai University, Kanagawa, Japan, in 1993 and 1996, respectively, and the Ph.D. degree in electrical and electronic engineering from Toyohashi University of Technology, Aichi, Japan, in 1999. He is now an Associate Professor in the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. His current research interests include nonlinear analog processing in neural networks and reaction-diffusion systems as well

as design and applications of neuromorphic VLSIs.

Yoshihito Amemiya received the B.E., M.E., and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1970, 1972, and 1975, respectively. He joined NTT Musashino Laboratories in 1975, where he worked on the development of silicon process technologies for high-speed logic LSIs. From 1983 to 1993, he was with NTT Atsugi Laboratories and developed bipolar and CMOS circuits for Boolean logic LSIs, neural network LSIs, and cellular automaton LSIs. Since 1993, he

has been a Professor with the Department of Electrical Engineering, Hokkaido University, Sapporo. His research interests are in the fields of silicon LSI circuits, signal processing devices based on nonlinear analog computation, logic systems consisting of single-electron circuits, and informationprocessing devices making use of quantum nanostructures.